RC Oscillator UMC

Overview

The agileOSC RC is based on a traditional architecture which allows for the frequency to be trimmed to remove the effects of process variation. This can also be configured as a Free Running Clock (FRC) where a high accuracy clock is not required.

Key Features

- • Start-up Time: Typ 10us

- • Frequency Range: 20KHz – 100MHz

- • Accuracy (Calibrated) Max = ? 5%

- • Current Consumption: Typ 100uA @ 10MHz

- • Configurable to your specification

- • Clean start-up

- • Trimmable frequency

- • Low power

- • Customizable design for simple SoC integration

- • Silicon Area – Please contact Agile Analog

Benefits

- DFT - Incorporates analog monitor (test) outputs to facilitate ATE test and debug

- On chip clock generator

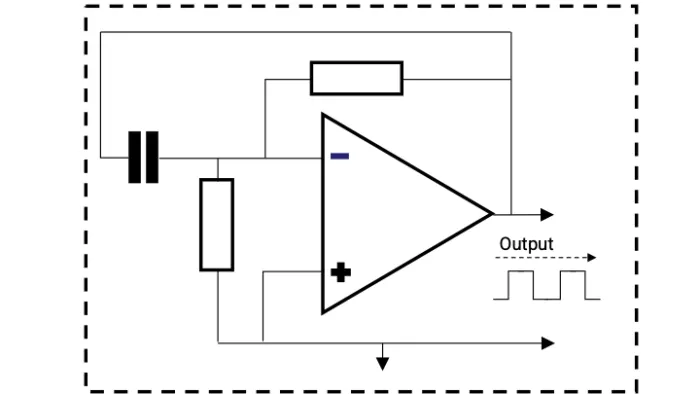

Block Diagram

Applications

- IoT, Security, Automotive, AI, SoCs, ASICs

Deliverables

- Datasheet

- Testing and Integration Guide

- Verilog Models

- Floorplan (LEF)

- Timing models (LIB)

- Netlist (CDL)

- Layout (GDS)

- Physical Verification Report

- Design Report

Technical Specifications

Foundry, Node

GlobalFoundries

Maturity

Available on request

Availability

Now

UMC

Pre-Silicon:

14nm

,

22nm

,

28nm

,

28nm

HLP

,

28nm

HPC

,

28nm

HPM

,

28nm

LP

,

40nm

,

40nm

LP

,

55nm

,

65nm

LL

,

65nm

LP

,

65nm

SP

,

80nm

,

90nm

G

,

90nm

LL

,

90nm

SP

,

110nm

,

130nm

,

150nm

,

162nm