The CODA980 is a Chips&Media’ enhanced video codec IP that supports AVC/H.264 Highprofile encoding offering improved video quality at lower bitrates. The core allows full HD video to be encoded, as well as offering full HD decoding capabilities with multiple formats including H.264, MPEG2/4, VC-1, AVS, MVC, VP8, and Theora.

It is an ideal solution for a wide range of consumer applications from Home entertainment to networking and portable multimedia markets.

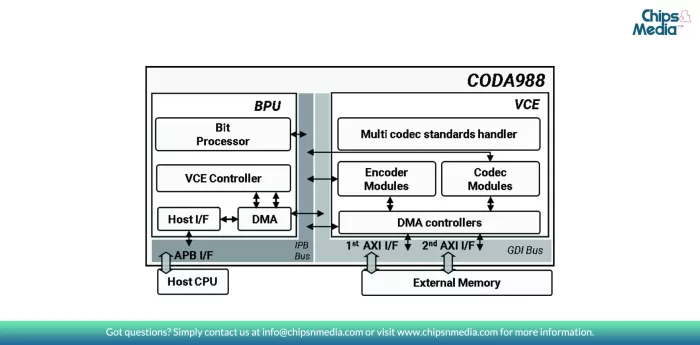

CODA988 - H.264, MVC, VP8, MPEG-1/2/4, VC-1, AVS, AVS+, H.263, Sorenson Decoding and encoding support at 1080p 60fps

Overview

Key Features

- Supported standards for Decoder

- ISO/IEC 14496-10 AVC/H.264 BP/MP/HP@L4.2

- ISO/IEC 14496-10/5 MVC Stereo High Profile@L4.1

- ISO/IEC 14496-2 MPEG-4 SP,ASP@L6

- SMPTE 421M-2006 VC-1 SP/MP/AP@L3

- ISO/IEC 13818-2 MPEG-2 MP@HL

- ITU-T H.263(Annex I,J,K,T)

- AVS Jizhun @L6.2

- AVS+ Guangdian @L6.2

- On2 VP8

- Sorenson Spark

- Theora

- Supported standards for Encoder

- ISO/IEC 14496-10 AVC/H.264 BP/MP/HP@L4.2

- ISO/IEC 14496-10/5 MVC Stereo High Profile@L4.1

- ISO/IEC 14496-2 MPEG-4 SP@L6

- ITU-T H.263(Annex J,K,T)

- Supported Max. Resolution

- Supports up to 2048x2048 resolution

- Performance

- Single-stream

- H.264 HD(1920x1080p) 30fps decoding at <133MHz core clock

- H.264 HD(1920x1080p) 60fps decoding at <266MHz core clock

- H.264 HD(1920x1080p) 30fps encoding at <133MHz core clock

- H.264 HD(1920x1080p) 60fps encoding at <266MHz core clock

- Multi-stream

- Dual H.264 HD(1920x1080p) 30fps decoding at <266MHz core clock

- Dual H.264 HD(1920x1080p) 30fps encoding at <266MHz core clock

- 6SD/D1(NTSC&PAL) 30fps decoding at <133MHz core clock

- Full HD(1080p) encoding and decoding at <266MHz core clock

- Encoding Tools

- Selective [+/-64,+/-48] Quarter-pel and half-pel accuracy motion estimation using a full- search algorithm

- Flexible bit-rate control

- CBR

- VBR

- Fixed QP

- CABAC/CAVLC for AVC/H.264

- Built-in pre- rotation/mirroring function

- 90xn degree rotation

- Vertical/horizontal mirroring

- Decoding Tools

- CABAC/CAVLC for AVC/H.264

- MPEG-4 AC/DC prediction

- AVC/H.264 intra-prediction

- In-loop deblocking filter for H.264, H.263, and AVS

- Overlapped smoothing filter for VC-1

- Built-in post-processing function

- 90xn degree rotation

- Vertical/horizontal mirroring

- De-ringing

- De-blocking filter for MPEG-2/4

- Interface

- AMBA 32-bit APB interface for Host CPU

- AMBA 64-bit AXI interface for the external memory

- Provides high performance for decoding or encoding at resolution of 1080p120fps(up to 4K 30fps)

- Supports MVC(Multi-view Video Coding) for Blu-ray 3D

- Supports VP8(WebM), Theora as well as H.264 for HTML5

- Full coverage of streams on a web browser and internet

- Delivers high-quality encoding capability for video communication or real-time transcoding

- Pre-configurable decoder format enabling SoC designers to optimize for area and power

- Simultaneous decoding or encoding of the multi-channel, multi-format stream.

- Memory challenge scheme including Tiled buffer map and 2D smart Cache

- Ultra-low-power hardware architecture using multi-level clock gating

- Low host CPU resources under 1MIPS

- Proven performance with a system-level design that minimizes risk and time-to-market

- Fully verified synthesizable RTL source code

- RTL test bench

- S/W User Guide

- Datasheet/Integration Guide

- Verification Guide

- Evaluation platform

Benefits

Block Diagram

Deliverables

Technical Specifications

Maturity

Now in mass production

Availability

Available

Related IPs

- H.264, MVC, VP8, MPEG-1/2/4, VC-1, AVS, AVS+, H.263, and Sorenson decoder HW IP for 2Kp60, 4:2:0

- HEVC/H.265, H.264 and AVS2 Multi format Decoder IP for 4K 60fps

- HEVC/H.265, H.264, VP9 and AVS2 Multi format Decoder IP for 4K 60fps

- HEVC/H.265, H.264, VP9, AV1 and AVS2 Multi format Decoder IP for 4K 60fps

- Scalable UHD H.264 Encoder - Ultra-High Throughput, Intra frames (IDR) encoding

- HEVC/H.265, H.264 Multi format Codec IP for 4K 60fps