Random Number Generator IP

Welcome to the ultimate Random Number Generator IP hub! Explore our vast directory of Random Number Generator IP

All offers in

Random Number Generator IP

Filter

Compare

17

Random Number Generator IP

from 9 vendors

(1

-

10)

-

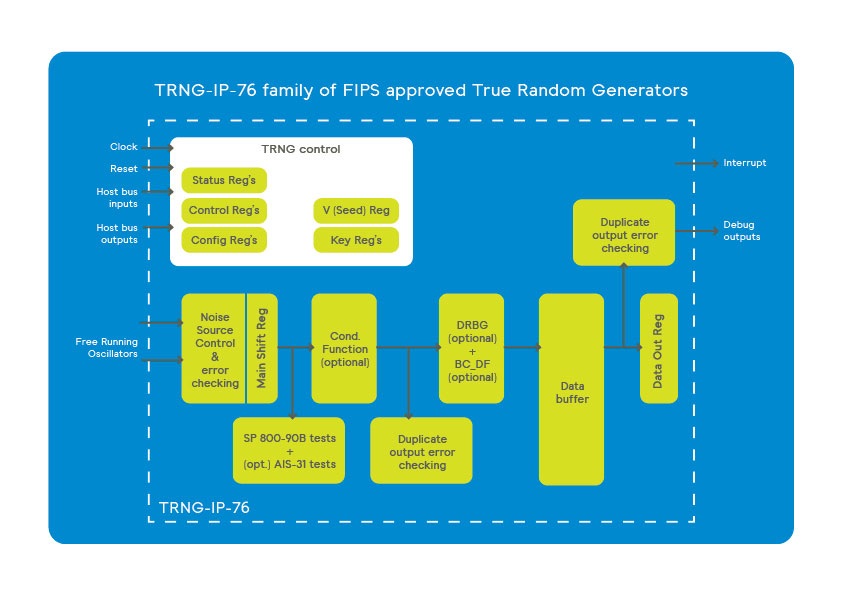

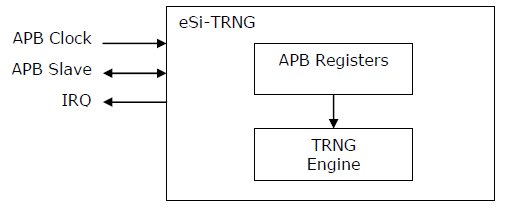

True Random Number Generator

- Patented test circuits on the oscillators to detect lockingto periodic signals.

- Repeating output data detection on NRBG and DRBG (compliant with [FIPS 140-2]).

- Hardware implemented ‘Repetition Count’ and ‘Adaptive Proportion’ tests on the Noise Source (compliant with [SP 800-90B]).

- Continuous tests on the Noise Source (compliant with [AIS-31]): ‘monobit test’, ‘poker test’, ‘runs test’, ‘longruns test’ and ‘Noise Source failure’.

-

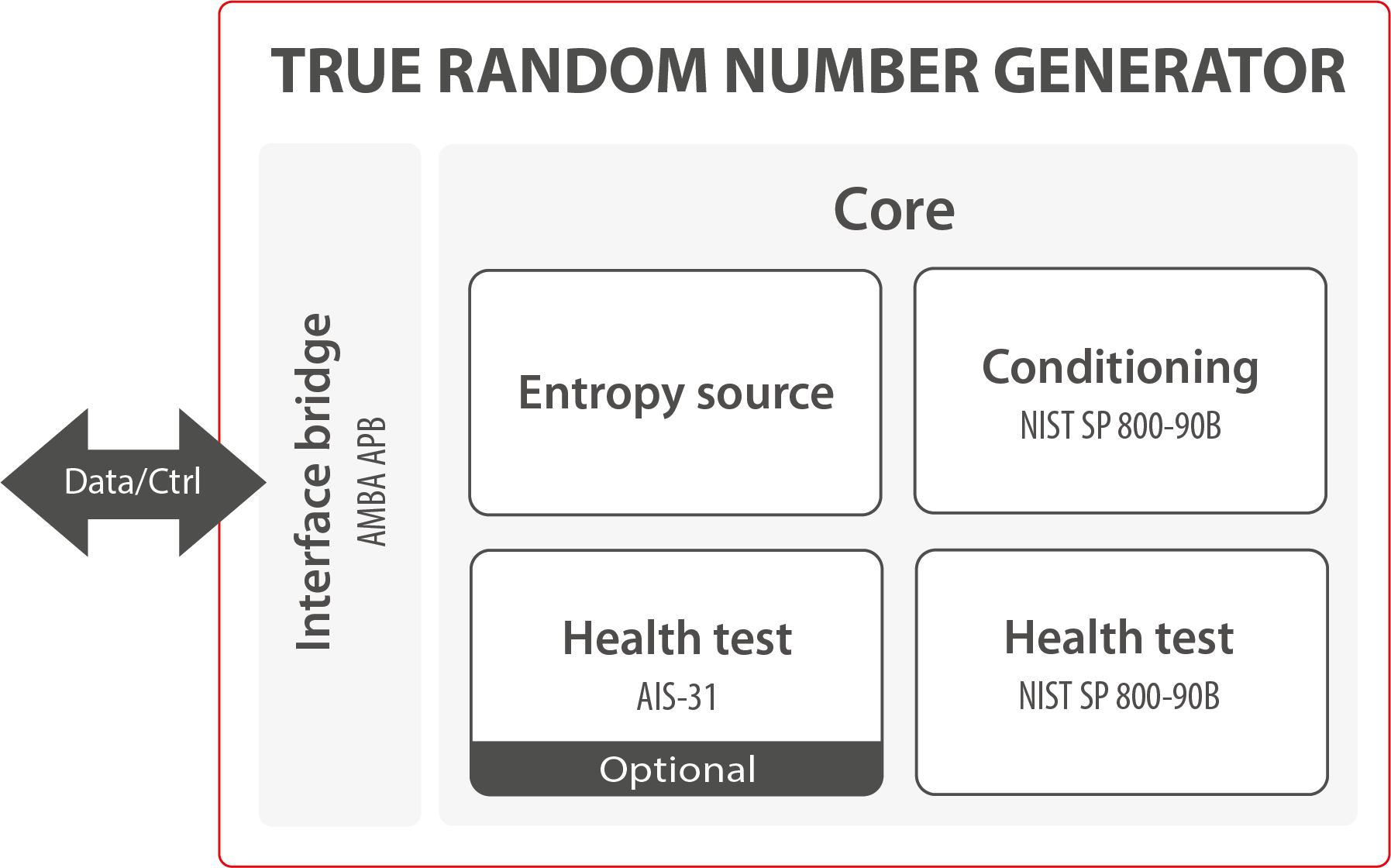

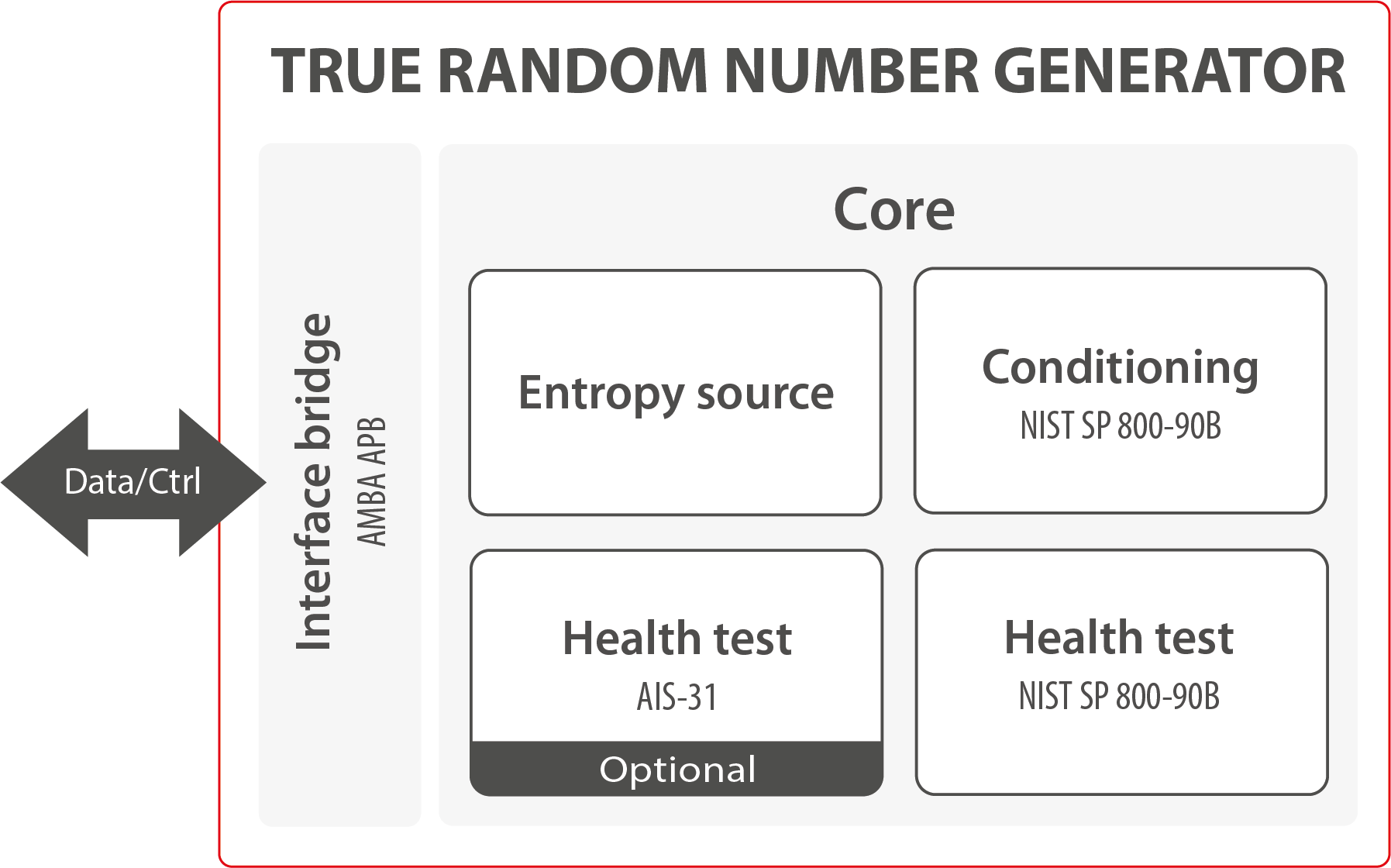

True Random Number Generator

- NIST 800-90B compliant

- AIS-31 start-up and on-line tests (optional)

- Passed NIST 800-22, 90B and AIS31 test suites

-

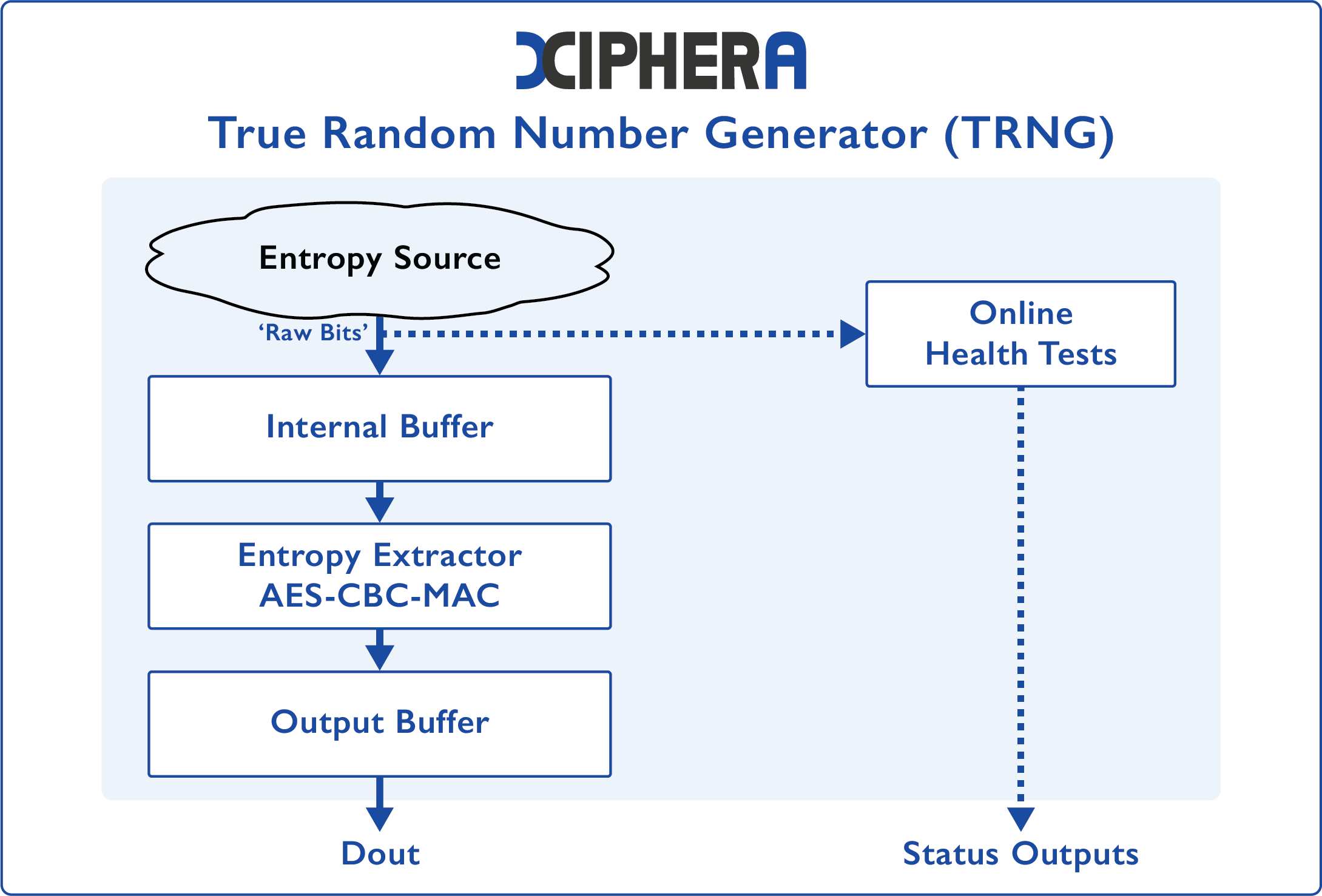

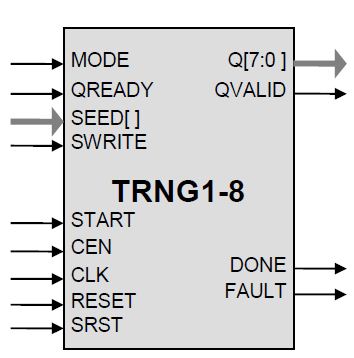

True Random Number Generator (TRNG)

- Compact Size

- Autonomous Operation

- Parameterizability

-

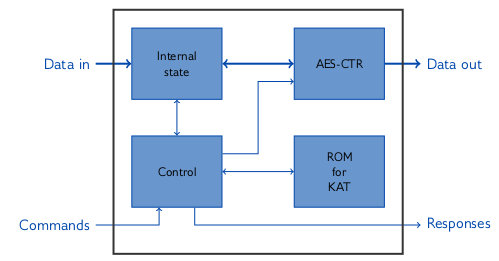

Deterministic Random Bit Generator (DRBG)

- NIST 800-90A/B/C compliant

- Health test

- AES-CTR based (CTR_DRBG)

-

TRNG fully compliant with NIST 800-22

- ASIC or FPGA target

- Generates 256 random bits at a time

- Multiple ring oscillators with post processing for true random bit generation

- Fully compliant with latest NIST 800-22 800-22 and Diehard Random test suite

-

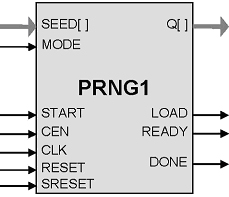

True Random and Pseudorandom Number Generator

- Satisfies Federal Information Processing Standard (FIPS) Publication 140-2 Annex C (“approved” random number generator) from the US National Institute of Standards and Technology (NIST). Passes the requirements of the NIST SP 800-22.

- High security (128 bit entropy; 256 version available)

- Initial seed provided from internal entropy source

- Automatic re-seeding

-

Cryptographically Secure Pseudo Random number Generator IP Core

- Generates cryptographically secure pseudo-random numbers

- Uses the CTR_DRBG algorithm per NIST publication SP800-90

- Generates 128-bit data blocks with 8, 16, 32, 64 or 128-bit wide data interface

- Provides security strength of 128,192 and 256 bits

-

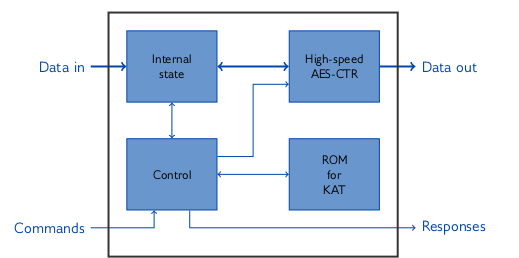

Pseudo Random Number Generator, high-speed version (AES256_CTR_DRBG)

- Fully digital design

- Portable to any ASIC or FPGA technology

- Fully standard compliant

-

Pseudo Random Number Generator, balanced version (AES256_CTR_DRBG)

- Balanced Between Speed and Resource Requirements: XIP8103B can achieve over 2 Gbps throughput, while consuming only about 4000 Lookup Tables (LUTs) in a typical FPGA implementation.

- Versatility: XIP8103B supports the forward prediction resistance mode, which can be set on and off between output generation, as well as the use of personalization strings and additional inputs for instantiation and reseeding.

- Standard Compliance: XIP8103B is compliant with the NIST SP800-90A specification.

- XIP8103B can be combined with Xiphera’s NIST SP800-90Bcompliant XIP8001B to form a NIST SP800-90C compliant Random Bit Generator (RBG).

-

Digital True Random Number Generator (TRNG), compliant with NIST SP800-90

- Fully Digital and based on standard cells

- Compliant with: AIS-31 (PTG.1 to PTG.3), NIST FIPS 140-3, NIST SP 800-90, GM/T 0005-2015

- Robust against process, temperature and voltage variations

- Post-silicon fine tuning to ensure high-level functional safety