SD PHY IP

Welcome to the ultimate SD PHY IP hub! Explore our vast directory of SD PHY IP

All offers in

SD PHY IP

Filter

Compare

29

SD PHY IP

from 5 vendors

(1

-

10)

-

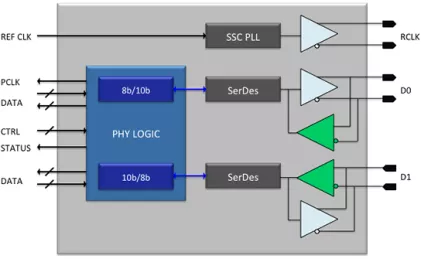

SD 4.0 UHS-II PHY TSMC 28nm HPM North-South

- Compliant with SD Specifications Part 1 UHS-II Addendum v1

- Supports data rate between 390 Mbps to 1.56 Gbps per lane

- Supports peak interface speed of 3.12 Gbps in Half-duplex mode; 1.56 Gbps in Full-duplex mode

- Sub-LVDS differential PHY signaling

-

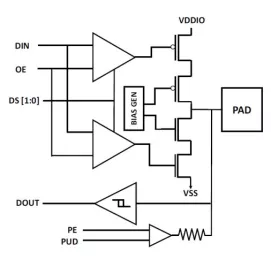

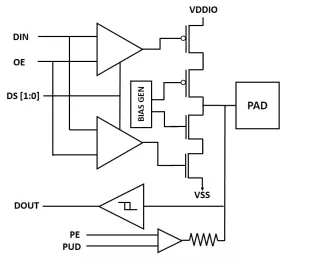

1.8V/3.3V Switchable GPIO With 5V I2C Open - Drain & Analog Cells in Samsung 11nm LPP

- Multi-voltage 1.8V / 3.3V switchable operation

- 4 selectable drive strengths (25-235 MHz @ 1.8V, 10pF

- Full-speed output enable

-

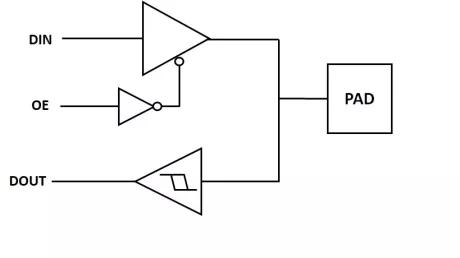

Secure Digital I/O offerings

- Secure Digital

- Physical Features

-

1.8V/3.3V Switchable GPIO With 5V I2C Open Drain & Analog in 16/12nm

- Multi-voltage 1.8V / 3.3V switchable operation

- 4 selectable drive strengths (25-235MHz @1.8V, 10pF)

- Full-speed output enable

- Independent power sequencing

-

SD 4.0 UHS-II PHY in TSMC 40LP

- Compliant to SD Specifications Part 1 UHS-II Specification Volume 2: PHY* and SD Specifications Part 1 UHS II

- Specification Volume 1: System and Protocol”

- Per lane data rate between 390Mb/s to 1.56Gb/s

- Supports peak interface speed of 3.12Gb/s (Half-duplex); 1.56Gb/s in Full-duplex mode

-

TSMC N3P 1.8V IO Platform supporting cells

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

TSMC N3P SD/eMMC PHY North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 7FF, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 6FF, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution

-

SD/eMMC - TSMC 28HPM, North/South Poly Orientation

- Compliant with eMMC 5.1 HS400, SD 6.0 SDR104, DDR50, JESD8-7a (1.2V/1.8V) and JESD8c.01 (3.3V)

- Fully integrated hard macro with high speed IOs and DLL/delay lines

- Fine resolution DLL/delay lines for HS400 strobe and HS200/SDR104 auto-tuning

- Easy to integrate with the highly optimized Synopsys SD/eMMC Host Controller IP, providing a complete low risk solution