eMMC Controller IP

Welcome to the ultimate eMMC Controller IP hub! Explore our vast directory of eMMC Controller IP

All offers in

eMMC Controller IP

Filter

Compare

17

eMMC Controller IP

from 9 vendors

(1

-

10)

-

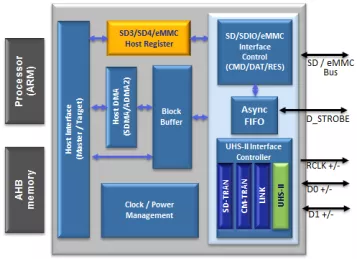

eMMC 5.1 Host Controller

- Compliant with eMMC Specification Version 5.0

- Supports one of the following System/Host Interfaces: AHB, AXI or OCP

-

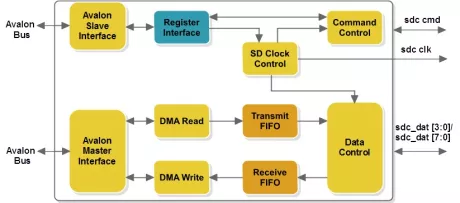

SD/eMMC Host Controller

- Supports selection between SD and eMMC

- Supports CRC7 and CRC16 generation and verification on Hardware

- Supports multiple block transfer

-

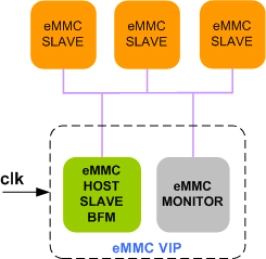

eMMC Verification IP

- Supports eMMC standard JESD84-A441, JESD84-B45, JESD84-B50, JESD84-B51 and JESD84-B51A specification.

- Supports stream transfer operations.

- Supports three different data width bus modes

- 1-bit(default)

-

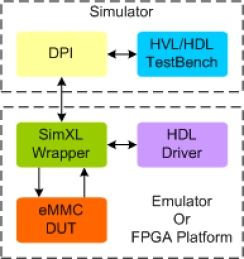

eMMC Synthesizable Transactor

- Supports eMMC standard JESD84-A441, JESD84-B45, JESD84-B50, JESD84-B51 and JESD84-B51A specification.

- Supports stream transfer operations.

- Supports three different data width bus modes

- 1-bit(default)

-

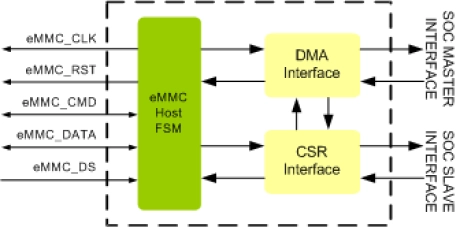

eMMC Host Controller IIP

- Compliant with JESD84-B50 Specification and earlier versions

- Compliant with JEDEC eMMC CQHCI for Command Queuing

- SD host controller Specification 6.0 compliant

- Supports different data bus width modes : 1-bit, 4-bit, 8-bit.

-

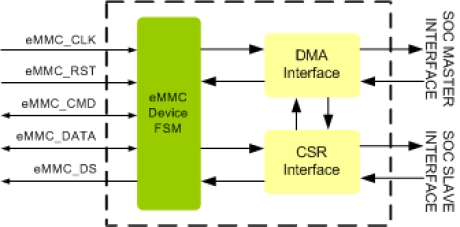

eMMC Device Controller IIP

- Compliant with JESD84-B51 Specification and earlier versions

- Compliant with JEDEC eMMC CQHCI for Command Queuing

- Supports different data bus width modes : 1-bit, 4-bit, 8-bit.

- Supports Command queuing

-

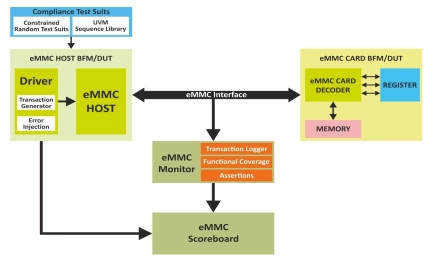

eMMC v5.1/A Verification IP

- Compliant with JEDEC eMMC version JESD84 - B51 and JESD84 – B51A.

- Supports eMMC devices from all leading vendors.

- Supports configuration for both host and device.

- Support all data widths 1x, 4x, and 8x.

-

SD/eMMC Lite Host Controller IP

- Compliant with the SD 6.0, SDIO 4.10 and eMMC 5.1 specifications and earlier versions

- Supports advanced eMMC features including HS400 mode and built-in CQE with priority sensitive scheduling algorithm for high performance

- Low power features with power gating and multi-power rails

- Supports the host controller interface (HCI) specification for SD ensuring the usability of standard software drivers with support for SDMA, ADMA2 and ADMA3 modes

-

SD/eMMC Host Controller IP

- Compliant with the SD 6.0, SDIO 4.10 and eMMC 5.1 specifications and earlier versions

- Supports advanced eMMC features including HS400 mode and built-in CQE with priority sensitive scheduling algorithm for high performance

- Low power features with power gating and multi-power rails

- Supports the host controller interface (HCI) specification for SD ensuring the usability of standard software drivers with support for SDMA, ADMA2 and ADMA3 modes

-

SD/eMMC Crypto Host Controller

- Compliant with the SD 6.0, SDIO 4.10 and eMMC 5.1 specifications and earlier versions

- Supports advanced eMMC features including HS400 mode and built-in CQE with priority sensitive scheduling algorithm for high performance

- Low power features with power gating and multi-power rails

- Supports the host controller interface (HCI) specification for SD ensuring the usability of standard software drivers with support for SDMA, ADMA2 and ADMA3 modes