A PWM sigma-delta modulator is a special type of 1-bit sigma-delta modulator that produces a pulse width modulated (PWM) output signal with a fixed repetition frequency. A fixed repetition frequency makes the output signal insensitive to typical problems associated with (continuous time) sigma-delta converters, such as non-linear inter symbol interference (ISI) and kickback noise on the reference of the DAC.

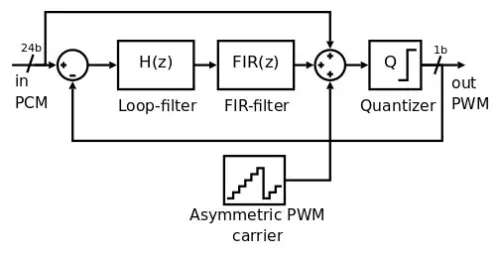

This IP block implements a digital PWM sigma-delta modulator consisting of a fifth-order loop filter, followed by a 16 taps moving average filter, a sawtooth carrier injection (with a frequency of fCLK/16) and a 1-bit quantizer.

PWM sigma-delta modulator

Overview

Key Features

- 117 dB dynamic range

- -120 dBFSA inband noise

- ISI insensitive bit stream

- No signal dependent kick back on DAC reference

- Multi bit advantages with a single bit modulator

- Hardware costs ~ 700 gates

- 0.018mm2 in 0.14μm CMOS

- Silicon proven

Block Diagram

Applications

- high accuracy PCM to PWM conversion

- signal generation for Class-D amplifiers

- D/A converters

- Audio subsystems

- Audio amplifiers with digital inputs

- Ideal in combination with FIRDAC (114dB DR measured)

- FPGA solution with discrete DAC (110dB DR measured)

Technical Specifications

Maturity

silicon proven