The LLEMAC-1G implements an Ethernet Media Access Controller compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications. Featuring extremely low egress and ingress latency, the core is ideal for the implementation of TSN Ethernet nodes, live streaming and other devices requiring minimum latency in the reception and transition of Ethernet frames.

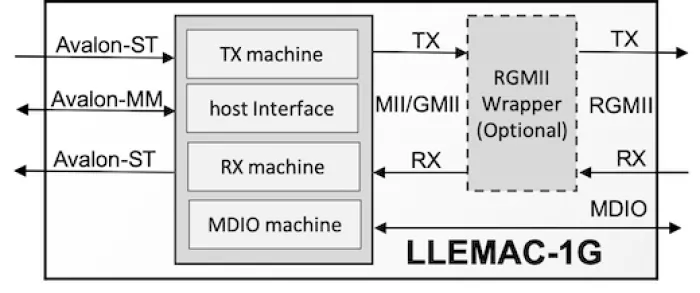

The core supports full-duplex operation, supports jumbo frames, provides statistics counters, and it is easy to integrate and implement. The LLEMAC-1G exchanges data with the host system via a byte-wide streaming interfaces, and connects to the external PHY via an MII, GMII or RGMII interfaces. An independently clocked, 32-bit wide memory mapped interface provides access to the cores control and status registers. The default core interfaces comply to the Avalon standard, but AMBA™ AHB or AXI can also be made available upon request.

Low-Latency 10/100/1000 Ethernet MAC

Overview

Key Features

- Low-Latency Ethernet MAC

- Supports IEEE 802.3

- Enables high-precision syn-chronization in TSN networks

- Egress latency:

- Tx clock cycles

- Ingress latency: 6 Rx clock cycles

- Full duplex point-to-point links

- Easy System Integration

- Autonomous operation, re-quires no host assistance once programmed

- Host Interfaces

- Avalon-MM: memory mapped

- Avalon-ST: stream

- PHY Interfaces

- Media Independent Interface (MII) for 10/100Mbps

- Gigabit Media Independent Interface (GMII) for 1Gbps

- Reduced Gigabit Media Inde-pendent Interface (RGMII) for 10/100/1000 Mbps

- MDIO interface for PHY con-figuration and management

Block Diagram

Applications

- The EMAC-1G can be used tin any SoC design requiring Ethernet connectivity.

Deliverables

- Source code Verilog RTL or targeted netlist

- Testbench

- Sample synthesis and simula-tion scripts

- Comprehensive documentation

Technical Specifications

Maturity

Production Proven

Availability

Now