JESD207 Synthesizable Transactor provides a smart way to verify the JESD207 component of a SOC or a ASIC in Emulator or FPGA platform. The SmartDV's JESD207 Synthesizable Transactor is fully compliant with standard JESD207 Specification and provides the following features.

JESD207 Synthesizable Transactor

Overview

Key Features

- Follows JESD207 specification

- Supports BBIC and RFIC Mode

- Supports half duplex data transfer

- Supports DDR source synchronous data transfer timing

- Supports both data path transaction and control plane transactions

- Supports data path transaction

- Supports transmit burst and receive burst

- Supports both 10bits and 12 bits sample width

- Supports 2 way interleave and 4 way interleave transactions

- Supports 1T1R,1T2R,2T2R systems

- Supports control plane transaction

- Supports 4 wires write and 4 wires read

- Supports 3 wires write and 3 wires read

- 1bit command plus 7bit address control field format

- Serial clock can be stopped between transactions,reducing control plane power consumption to negligible levels

- Extended data tranactions

- Supports various kinds of errors

- Mixed data error

- Invalid address error

- Compatible with testbench writing using SmartDV's VIP

- All UVM sequences/testcases written with VIP can be reused

- Runs in every major emulators environment

- Runs in custom FPGA platforms

- Synthesizable transactors

- Complete regression suite containing all the JESD207 testcases

- Examples showing how to connect and usage of Synthesiable VIP

- Detailed documentation of all DPI, class, task and functions used in verification env

- Documentation also contains User's Guide and Release notes

Benefits

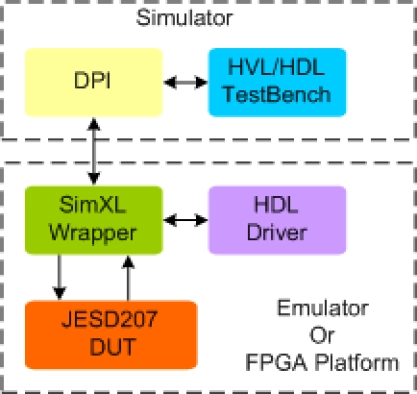

Block Diagram