The AXIOM_LLSDADC100dB is a low power variant of our high-resolution sigma-delta analog-to-digital converter family. It achieves a dynamic range of more than 100dB, at a power consumption only 1.6mW.

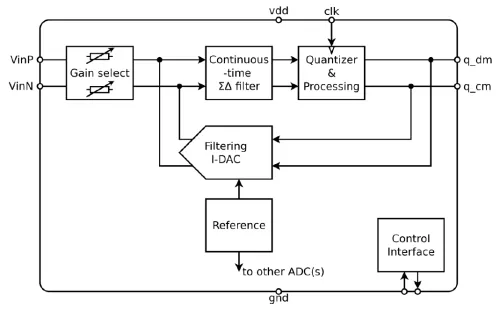

The latency of the ADC is only one clock cycle (40ns at 25MHz), which makes the converter ideally suited for application in control loops. The low latency is enabled by feeding the bitstream output back to the input via a DAC with build-in filtering. This creates a “tracking ADC behavior”, where the output accurately tracks the input signal inside the signal bandwidth. Next to enabling low latency, the filtering DAC also makes the system robust towards jitter and other error sources typically associated with 1-bit converters.

The AXIOM_LLSDADC100dB can convert both single-ended and differential signals with high accuracy. Next to this it can convert signals with amplitudes and biasing levels well outside its own supply level, by using external resistors acting as level shifters.

High Resolution Low Latency Sigma-Delta ADC

Overview

Key Features

- High dynamic range: >100dBA (20Hz – 20kHz)

- Low power: 1.6mW per ADC

- Low Area: 0.3mm2 per ADC

- Low latency: only one clock period (40ns)

- Low noise reference without external components

- Supports wide common mode range (true ground to supply & capacitive coupling)

- Supports both differential and single-ended input

- Supports 4 internal gain settings

- Using external resistors allows:

- Additional gain settings

- Extended input voltage range, well outside supply voltage range

- Silicon proven in 0.14µm CMOS

Benefits

- The AXIOM_LLSDADC100dB has an extremely low latency of only one clock cycle (40ns) with a dynamic range of 100dB. Thanks to the resistive inputs the converter is able to convert signal far beyond the supply rails and is a friendly load for the source. The converter converters common mode and differential mode signals simultaneously and indepently.

Block Diagram

Applications

- High-quality audio ADC & DAC (codec)

- Digital control loops (enabled by its low latency)

- Digital (Class-D) Amplifier

- Noise cancellation

- Sensor read-out

- Instrumentation

Deliverables

- Behavioral model (VHDL/Verilog/Simulink)

- Netlist (CDL)

- Layout (GDS2)

- Abstract (LEF)

- Checks (DRC/LVS/ANT)

- RTL (VHDL)

- Module header (INTERFACE, VHDL)

- Timing & interface (SDC & LIB)

- Design documentation (PDF)

- Integration documentation (PDF)

Technical Specifications

Foundry, Node

140nm CMOS

Maturity

The design has been silicon proven and ready for mass production

Related IPs

- High Throughput and Low Latency Data Compression Engine

- High Performance / Low Power Microcontroller Core

- 24-Bit High resolution sigma-delta charge-redistribution DAC

- 2D (vector graphics) & 3D GPU IP A GPU IP combining 3D and 2D rendering features with high performance, low power consumption, and minimum CPU load

- Low latency H.264(AVC) Encoder IP Core

- High Accuracy Low Latency Sigma-Delta ADC