The ColdFire V4 Processor is a high-performance implementation of the ubiquitous ColdFire architecture from Freescale Semiconductor, offering over 500 DMIPS of performance. Fully code compatible with ColdFire V1 and V2 devices, the ColdFire V4 Core offers high-end features such as cache and Memory Management Unit (MMU), plus advanced arithmetic units including hardware divider (DIV), enhanced MAC (EMAC), and an optional Floating Point Unit (FPU).

Like all ColdFire processor cores available from Silvaco, the ColdFire V4 Core is a production-proven design. The ColdFire V4 Core is the same IP implemented in Freescale's MCF5441x microcontrollers. By either including or excluding the FPU, you can configure the ColdFire V4 Core to match either the V4e or V4m processor configuration used in Freescale MCF54xx devices. And, like the ColdFire V1 and V2 cores, the ColdFire V4 Core benefits from the extensive ecosystem of development systems, tools, and software supporting the ColdFire architecture.

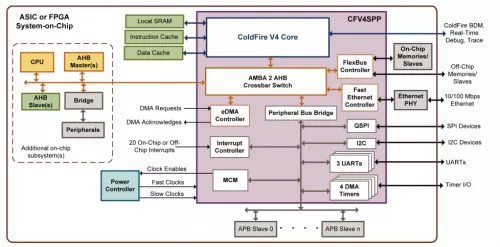

ColdFire V4 SPP Processor Platform

Overview

Key Features

- On-board peripherals and their features include:

- FlexBus Controller

- Connects up to 6 on-chip or off-chip memories/devices

- Independently programmable transfer characteristics for each

- device (wait states, address setup/hold)

- Enhanced DMA (eDMA) Controller

- 16 independently programmable DMA channels

- Programmable channel arbitration modes

- Support for channel linking and scatter/gather operation

- Fast Ethernet Controller

- 10/100 Mbps Ethernet support

- Half and full-duplex modes

- Media Independent Interface (MII) or 7-wire interface to

- Ethernet PHY

- Interrupt Controller

- 64 programmable interrupt sources, 20 of which are available

- for external interrupts

- Unique vector for each interrupt source

- Support for low-power mode wake-up

- Queued SPI (QSPI) module

- Programmable queue for up to 16 SPI transfers

- Four chip-select lines for up to 16 devices

- Programmable baud rate, before-and-after transfer delays,

- clock phase and polarity

- I2C interface module

- Support for the original Philips I2C bus protocol

- Support for baud rates up to 3.4 Mbps

- 3 UARTS

- Programmable clock source, data formats, and modes

- (normal/loopback)

- Error detection

- Four maskable interrupt conditions

- 4 DMA Timer modules

- Programmable clock source

- Programmable prescaler

- Programmable interrupt or DMA request upon timer event

- Miscellaneous Control Module (MCM)

- Software watchdog timer

- Reset status, low-power mode control, and core fault status

- registers

Benefits

- The ColdFire V4 Core achieves best-in-class 32-bit processor performance through a combination of features including a 9-stage pipeline with limited superscalar (dual-issue) instruction execution. The 9-stage pipeline consists of a 4-stage Instruction Fetch Pipeline (IFP) and 5-stage Operand Execution Pipeline (OEP) decoupled by a FIFO instruction buffer. The optional FPU executes instructions in parallel with the OEP. Separate clocks for the CPU and system bus enable the V4 ColdFire Core to operate at a higher frequency than the rest of the system.

- The ColdFire V4 Core achieves 1.54 DMIPS/MHz and can run at up to 345 MHz in a 90-nm process technology.

- Local RAM and cache, running at the CPU clock rate, further maximize system efficiency by reducing the overall number of system bus accesses, leaving more system bus bandwidth available for other system resources such as other another processor or DMA controller. The system bus is the industry standard AMBA 2 AHB. The ColdFire V4 Core includes both an AHB master port and an AHB slave port, which enables an external AHB master to access the ColdFire V4 local RAM, either while the ColdFire V4 Core is running or while it is in low-power STOP mode.

Block Diagram

Video

Putting the ColdFire Family to Work for You

Deliverables

- Verilog source code

- Integration testbench and tests

- Documentation

- Scripts for simulation and synthesis with commonly-used EDA

- tools

Technical Specifications

Maturity

Silicon Proven

Availability

Now