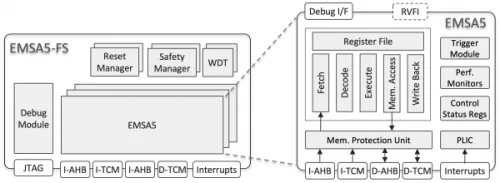

The EMSA5-FS is a processor core designed for functional safety. The fault-tolerant processor uses dual or triple instances of the EMSA5, an efficient 32-bit embedded processor IP core implementing the RISC-V Instruction Set Architecture (ISA).

The Harvard architecture EMSA5 processor implements a single-issue, in-order, 5-stage execution pipeline, supporting the RISC-V 32-bit base integer instruction set (RV32I), or the 32-bit base embedded instructions set (RV32E). EMSA5 can support machine and user privilege modes, and optionally the standard Multiply (M), Compressed (C), Control and Status Register (Zicsr), and Instruction-Fence (Zifencei) RISC-V extensions. The processor core communicates with the system via two 32-bit AHB-lite buses (one for data and one for instructions) and its interrupt lines.

Designed to meet the most stringent functional safety requirements, EMSA5-FS implements a memory protection unit, employs modular redundancy, uses error correction codes (ECC), and is delivered with sample reset and safety manager modules. Privileged operation modes provide a mechanism to isolate application user-mode processes from each other and from trusted code running in machine mode. The highly configurable memory protection unit enables memory partitioning, which provides protection by restricting access or specific types of access to memory and memory-mapped modules (e.g. peripherals). ECC protects the memories and buses and modular redundancy protects the internal processor modules. Finally, the safety manager provides logical and timing supervision and can be customized to meet the requirements of the end application.

Part of CAST’s family of processor cores, the EMSA5-FS processor core has been designed for easy reuse, has been rigorously verified, and is delivered with an ISO 26262 ASIL-D Ready certificate.

32-bit Embedded RISC-V Functional Safety Processor

Overview

Key Features

- Designed for Functional Safety

- ISO 26262 ASIL-D Ready Design

- Complete certification package including FMEDA and SAM documents

- Fail-safe features: Modular redundancy, ECC protection of b-ses, reset and safety manager modules

- Memory protection unit with up to 16 regions of configurable size

- Versions:

- EMSA5-FS-T (TMR),

- EMSA5-FS-D (DMR), and

- EMSA5-FS-L (DMR in lockstep).

- Efficient Embedded RISC-V Processor

- Single-issue, in order, 5-stage pipeline

- Harvard architecture with separate Instruction and Data 32-bit AHB-Lite buses

- RV32[I/E][M][C][Zicsr][Zifencei] ISA

- 32 or 16 32-bit integer registers (16 with the optional E extension)

- Optional Compressed (16 bit encoding) instructions (C extension)

- Optional Multiply/Divide instructions (M extension)

- User and Machine Privilege Modes

- Sixteen interrupt lines, extendable with the use of an external interrupt controller, and one Non-Maskable Interrupt (NMI) line

- Powerful Debug Features

- Configurable Hardware Performance Monitor

- Support for RISC-V External Debug Support Version 0.13.2 including a Configurable Trigger Module

- Optionally delivered with an Advanced Integrated JTAG Debug Controller

- Easy Software Development and SoC Integration

- Compatible with industry-standard debug pods under open-source Eclipse-based or commercially available IDEs

- Exploits the wide ecosystem of RISC-V toolchains and libraries

- Available FPGA development kit for rapid prototyping and evaluation

- Optional off-the-shelf platforms integrate the EMSA5-FS core with bus fabric and typical microcontroller peripherals such as GPIO, UART, Real-Time Clock, Timers, I2C, and SPI

- On-request custom-tailored integrated platforms using the EMSA5-FS core and CAST interconnect and peripheral cores

- The silicon resources requirements for the EMSA5-FS depend on its configuration. Core configurations using TMR start from 60k gates, and DMR configurations start from 40k gates. EMSA5-FS can run at frequencies exceeding 1GHz on advanced process nodes. Please contact CAST to get implementation data for your target configuration and technology.

- The core is available for ASICs in synthesizable Verilog source code or for FPGAs in optimized netlists. It includes everything required for successful implementation: extensive documentation, a testbench, a sample SoC design, sample synthesis and simulation scripts.

- Furthermore. a Safety Manual (SAM), a Failure Modes, Ef-fects and Diagnostics Analysis (FMEDA) document and the ASIL-D Ready certificate, issued by SGS-TUV Saar GmbH, are delivered with the core.

- Reference designs on FPGA boards are also available; contact CAST Sales for more information

Benefits

Block Diagram

Deliverables

Technical Specifications

Related IPs

- 32-bit RISC-V processor specifically designed for the Automotive and Functional Safety markets

- 32-bit RISC-V embedded processor with TÜV SÜD ISO 26262 ASIL B certification

- Low-power 32-bit RISC-V processor

- Ultra High Performance 32-bit RISC-V Embedded Processor

- 32-bit RISC-V High Performance Microcontroller Class Processor

- RISC-V ARC-V RMX-100 Ultra-low Power 32-bit Processor IP for Embedded Applications