Small is beautiful...

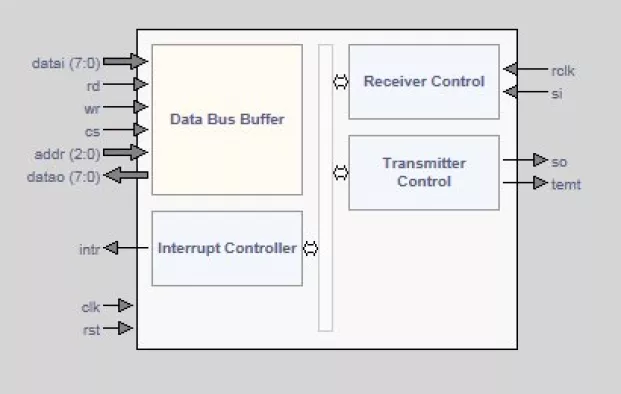

The DuART is one of the tiniest UART IP Cores available on the market.The DuART is a soft core of a Universal Asynchronous Receiver/Transmitter (UART). It performs serial-to-parallel conversion on data characters received from a peripheral device or a MODEM, and parallel-to-serial conversion on data characters received from the CPU. The CPU can read the complete status of the UART at any time during the functional operation. Reported status information includes the type and condition of the transfer operations performed by the UART, as well as any error conditions (overrun, framing). The DuART includes a programmable baud rate generator capable of dividing timing reference clock input by divisors of 1 to (216-1), and producing 16 × clock for driving internal transmitter logic. Provisions are also included to use this 16 × clock to drive receiver logic. The DuART has a processor-interrupt system. Interrupts can be programmed to user's requirements, minimizing computing required to handle the communications link.

The core is perfect for applications where the UART Core and microcontroller are clocked by the same clock signal and are implemented inside the same ASIC or FPGA chip, as well as for a standalone implementation, where several UARTs are required to be implemented inside a single chip and driven by some off-chip devices.

Tiny UART

Overview

Key Features

- Majority Voting Logic

- Adds or deletes standard asynchronous communication bits (start, stop, and parity) to or from the serial data

- In UART mode receiver and transmitter are double buffered to eliminate the need for precise synchronization between the CPU and serial data

- Independently controlled transmit, receive, line status, and data set interrupts

- 16 bit programmable baud generator

- False start bit detection

- Line break generation and detection. Internal diagnostic capabilities:

- Loop-back controls for communications link fault isolation

- Overrun, framing error detection

- Full prioritized interrupt system controls

- Technology independent HDL Source Code

- Fully synthesizable static design with no internal tri-state buffers

Block Diagram

Applications

- Serial Data communications applications

- Modem interface

- Embedded microprocessor boards

Deliverables

- HDL Source Code

- Testbench environment

- Automatic Simulation macros

- Tests with reference responses

- Synthesis scripts

- Technical documentation

- 12 months of technical support