The SHA-384/512 is a high-throughput, and compact hardware implementation of the SHA-384 and the SHA-512 cryptographic hash functions provisioned by the FIPS180-4 standard.

The core is designed for ease of use and integration and adheres to industry-best coding and verification practices. Technology mapping, and timing closure are trouble-free, as the core contains no multi-cycle or false paths, and uses only rising-edge-triggered D-type flip-flops, no tri-states, and a single-clock/reset domain. The SHA-384/512 core features a simple input and output data interface. Support for AMBA bus interfaces and integration with an external DMA are available as options.

The highly reliable SHA-384/512 has been production-proven in several ASIC and FPGAs designs.

SHA-384 and SHA-512 Secure Hash Crypto Engine

Overview

Key Features

- Custom-hardware accelerator for the SHA-384 and SHA-512 cryptographic hash functions

- Compliant to FIPS 180-4 with maximum message length up to (2128 – 1) bits

- High throughput:

- 81 clock-cycles per 1024-bit input block

- Throughput scaling with multiple clock instances.

- Small Silicon footprint: 15k-20k Gates

- Easy integration & implementation

- Fully synchronous, uses only the rising clock edge, single-clock domain, no false or multicycle timing paths, scan-ready, LINT-clean, reusable design

- Simple input and output interfaces optionally bridged to AMBA™ interfaces or integrated with a DMA engine.

- Available in VHDL or Verilog source code format, or as a targeted netlist for AMD/Xilinx, Intel FPGA, Lattice, Microsemi, or other FPGA devices

- Complete deliverables include test benches, C model, and test vector generator

- Multiple times production-proven in ASIC and FPGA designs

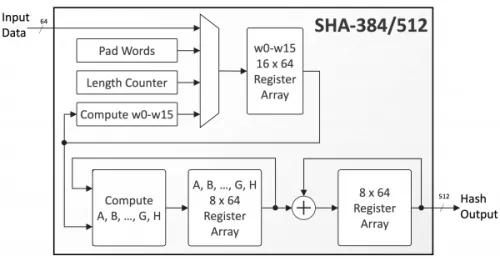

Block Diagram

Applications

- Electronic Funds Transfer

- Authenticated Electronic data transfer

- Encrypted data storage

Deliverables

- The core is available in RTL (VHDL or Verilog) source code or as a targeted FPGA netlist. Its deliverable package includes the following:

- Sophisticated self-checking HDL testbench

- C Model & test vector generator

- Sample simulation & synthesis scripts

- User documentation

Technical Specifications

Maturity

Production Proven

Availability

Now