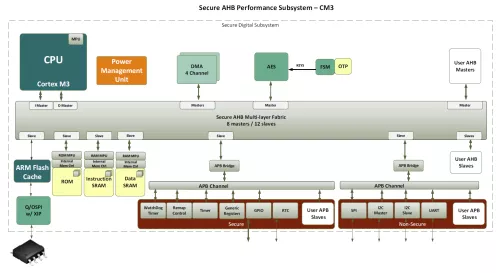

The Silvaco Secure AHB Performance Subsystem is a high-performance AHB subsystem that allows for a high level of hardware and software security. It integrates a security conscious processor, the ARM Cortex-M3, with a security conscious low power high-performance subsystem. Everything is pre-integrated with the necessary AHB and APB IP cores needed to run a small software kernel or a Real Time Operating System (RTOS). This subsystem is ideal for any deeply embedded system that requires enhanced security and protection from cyber-attacks and intrusions, such as IoT, smart sensors, smart controllers, and mixed signal devices.

Security in the Cortex-M3 is based on the MPU, Handler Mode, and privilege level. There are 8 memory ranges supported by the MPU and, it only regulates one master - the processor - in a multimaster system. To prevent additional masters from violating system integrity, the Secure AHB Subsystem adds the following IP:

• Secure AHB Fabric

• SRAM Programmable Memory MPU

• ROM Parameterized Memory MPU

The Secure AHB Fabric connects several AHB Masters (secure or non-secure) to several AHB Slaves (secure or non-secure) in a crossbar switch arrangement. In this system, only the processor can produce secure AHB transactions, and all other AHB Masters are always designated as non-secure . AHB Slaves are categorized by the Fabric as either secure or nonsecure, depending on the level of protection that is desired. A special case exists for memories, which are designated as nonsecure slaves by the Fabric. Security enforcement for memories is performed instead by the SRAM Programmable Memory MPU and/or the ROM Parameterized Memory MPU. This arrangement provides for greater flexibility for each physical memory - each memory may be divided into secure and nonsecure regions - and potentially reduces the number of memory instantiations in the system. The Secure AHB Fabric& Memory MPUs can be used stand-alone, or in conjunction with the ARM Cortex-M3’s Memory Protection Unit (MPU). The Secure Fabric can take care of all coarse memory security partitioning leaving more room in the MPUs for finer tuning.

Secure AHB Performance Subsystem - ARM M3

Overview

Key Features

- Processor Options

- ARM Cortex-M3 with low power logic, JTAG, MPU

- Optional Instruction/Data Mux (Von Neuman or Harvard Architecture)

- Optional ARM Flash Cache (order separately from ARM)

- Infrastructure

- CPU

- Secure AHB Bus Matrix / Decode – 8 masters, 12 slaves

- AHB to APB Bridge (2)

- JTAG

- Standard Peripherals

- 8,16,32-bit Internal SRAM Controller with MPU

- ROM with MPU

- Power Management Unit

- DMA (4 channels)

- AES with optional secure key loader

- Windowed Watchdog Timer

- Timers (2)

- Remap Register

- Real-Time Clock

- Configurable Peripherals

- Secure AHB Fabric Interconnect

- GPIO (width, interrupt capability)

- I2C Master

- I2C Slave

- SPI Master / Slave

- Quad SPI Master / Slave (Octal SPI Master optional) 16550 UART

- Generic Registers

- Hardware Security Features

- ARM Memory Protection Unit (MPU) & Privilege level

- SRAM & ROM MPUs

- AES H/W Encryption/Decryption

- Keys for AES can be in NV or OTP memory and directly loaded into AES registers (No processor access)

- AHB Fabric is parameterized so each master and slave can be designated as secure or non-secure

- If a non-secure AHB master attempts to access a secure AHB slave, the access is blocked, bus info is captured, and an interrupt can be generated

- Software

- An RTOS (such as Free RTOS) may be used

- Secure Flash Loader, Boot Loader

- Examples using AES, Secure Fabric, and MPU

- Interrupt and Fault Handlers

- Use of Main and Process Stacks

- Supervisory Call (SVC) examples

- Hardware Adaption Layer / Drivers

- AES, GPIO, QSPI, Timer, UART, Watchdog Timer

Benefits

- Quick development start up

- Low power plus performance to handle most IoT software

- Integration and software support available

- Cost effective

Block Diagram

Applications

- IoT Edge Devices

- Medical Devices

- Mixed Signal Digital - MEMS

- Smart Sensors, Smart Metering, Smart Lighting

- Health Monitors

- Home / Office

- Surveillance, Home Automation, Smart Thermostats

- Industrial

- Machine / Motor Control, System Health Monitoring

Deliverables

- Verilog RTL source code

- Test bench with test suites

- Documentation including User's Guide and Integration Guide

- Technology-independent synthesis constraints

Technical Specifications

Foundry, Node

all

Maturity

Silicon Proven

Availability

Now