Scatter-Gather DMA - AXI4-Stream to/from AXI4 Memory Map Transfers

Overview

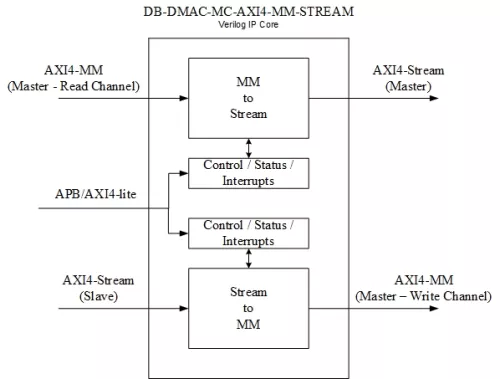

The Digital Blocks DB-DMAC-MC-AXI4-MM-STREAM Verilog RTL IP Core is a Multi-Channel Scatter-Gather DMA Controller that transfers data between AXI4 Memory Map and AXI4-Stream Interfaces.

Key Features

- 2 Dedicated DMA Channels, 1 each for data transfers for the following:

- Host Memory to Peripheral (AXI4-Memory Map to AXI4-Stream)

- Peripheral to Host Memory (AXI4-Stream to AXI4-Memory Map)

- DMA Channel Features:

- Scatter-Gather Descriptor Processor Engine

- Descriptor FIFO to queue descriptors

- Read & Write DMA Controller Engines

- Data FIFO

- Unaligned data transfers with byte realignment & using byte strobes

- Advanced algorithm mapping AXI4-Memory Map address to/from AXI4-Stream sideband TID, TDEST, TUSER

- Control / Status Registers accessible via APB/AXI4-Lite Interfaces

- Parameters for FIFO width and depth

- AXI4 Interfaces:

- AXI4-Memory Map Read Channel

- AXI4-Memory Map Write Channel

- Two AXI4-Stream Interfaces

- Programmable Data Bursts: 1, 4, 8, 16 (fixed) and 1 – 256 (AXI4)

- 4 KB boundary crossing detection & resizing of AXI transaction

- Arbiter allows 2 Descriptor Engines and DMA Data Read to share single AXI4-Memory Map Read Channel to Host Memory

- AXI4 Data Widths: 8 / 16 / 32 / 64 / 128 / 256 / 512 / 1024

- Interrupt Controller

- Configurations with more DMA Channels and AXI4-Stream Interfaces sharing same AXI4-Memory Map Read/Write Channels

Block Diagram

Deliverables

- Verilog RTL Source or technology-specific netlist.

- Comprehensive testbench suite with expected results.

- Synthesis scripts.

- Installation & Implementation Guide.

- Technical Reference Manual.

Technical Specifications

Maturity

Successful in Customer Implementations

Availability

Immediately

Related IPs

- AXI4-Stream to/from AXI Memory Map – 2 DMA Channels - Control by SGL Descriptors

- AXI4-Stream to/from AXI Memory Map – 2 DMA Channels - Control by SGL Commands Streams

- AXI4 to/from AXI4-Stream Scatter-Gather DMA

- AXI4-Stream to/from AXI Memory Map - AXI4-Stream Conversion to AXI Memory Map, 16 Channels

- AXI4-Stream to/from AXI Memory Map - AXI Memory Map Conversion to AXI4-Stream, 16 Channels

- AXI4 Memory-Mapped to/from AXI4-Stream DMA