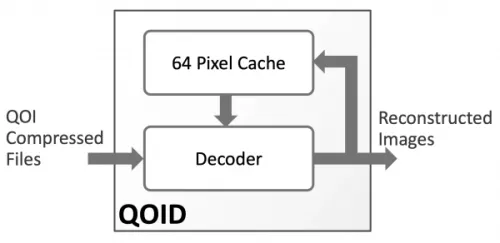

The QOID Core is a decoder that implements a highly-efficient, low-power, lossless image decompression engine compliant with the Quite OK Image format (QOI) specification, version 1.0.

The QOI algorithm compresses RGB or RGBA images with 8 bits per color without any loss. It has a compression efficiency close to that of the PNG compression, at a fraction of the computational complexity.

Capitalizing on the simplicity of the QOI algorithm, the QOID encoder core can decompress images at a very high speed and with minimal silicon resources. The core occupies approximately 15,000 equivalent NAND2 gates and can process one pixel per clock cycle. A single core instance can compress images at rates sufficient for UHD 4k30 video even in low-end FPGAs, 4k60 in mid-range FPGAs, and 8k30 or 60 in modern ASIC technologies.

The core is designed for ease of use and integration and adheres to coding and verification best practices. It requires no assistance from a host processor and uses simple handshake interfaces for input and output data. Technology mapping, timing closure, and scan insertion are trouble-free, as the core contains no multi-cycle or false paths, and uses only rising-edge-triggered D-type flip-flops, no tri-states, and a single-clock/reset domain. Its reliability and low risk have been proven through rigorous verification and FPGA validation.

QOI Lossless Image Decompression Core

Overview

Key Features

- Lossless Compression Decoder for the QOI Image Format

- UHD-capable. A single core can do 4k30 on FPGA and 8k on modern ASIC technologies

- Compact and Low-Power. Approximately 15,000 gates

- Supports 24-bit RGB and optionally 32-bit RGBA

- Available in VHDL or Verilog RTL source code or targeted FPGA netlist

Benefits

- UHD Capable Lossless Image Compression

- Tiny Silicon Footprint

Block Diagram

Applications

- Numerous applications can benefit from the tiny silicon footprint and ultra-low-power consumption of the QOI compression and decompression cores CAST offers. Typical uses include frame buffer compression for video processing SoCs; graphic elements or display buffer compression; and image storage and transmission for medical, aerospace, and other systems.

Deliverables

- VHDL or Verilog RTL Source, or Targeted FPGA Netlist

- Sophisticated self-checking Testbench

- Software Bit-Accurate Model

- Sample simulation and synthesis scripts

- Comprehensive user documentation

Technical Specifications

Availability

Now

Related IPs

- QOI Lossless Image Compression Core

- JPEG 2000 Encoder - Up to 16-bit per Component Lossy & Numerically Lossless Image & Video Compression

- Lossless JPEG Encoder - Up to 16-bit per Component Numerically Lossless Image & Video Compression

- JPEG-LS Lossless Image Encoder

- CCSDS 122.0-B-1 Encoder - Lossless and Lossy Image Data Compression with up to 16 bits Pixel Dynamic Range

- Scalable UHD JPEG 2000 Encoder - 8 up to 16 bits per Component Lossy or Numerically Lossless Image & Video Compression