JPEG-LS Lossless Image Encoder

The Lancero JPEG-LS Lossless Image Encoder IP Core is a efficient FPGA based implementation of the ITU T.87 lossless image compre…

Overview

The Lancero JPEG-LS Lossless Image Encoder IP Core is a highly efficient FPGA based implementation of the ITU T.87 lossless image compression standard. JPEG-LS performs better than JPEG-2000 in most lossless use cases but with less resource requirements and no need for external memory. Encoding requires less than one line of latency.

Key features

- Leading lossless image compression results for 8 to 16 bits image sample depths

- Less than one line of encoding latency

- Low resource count, no external memory needed. Scales to multiple instances is easy

- Pixel and data FIFO input/output or Avalon Streaming interface with back-pressure

- Accepts and encodes one pixel per clock cycle

- Configurable output data word width

- Configurable image sizes up to ultra-high definition and beyond

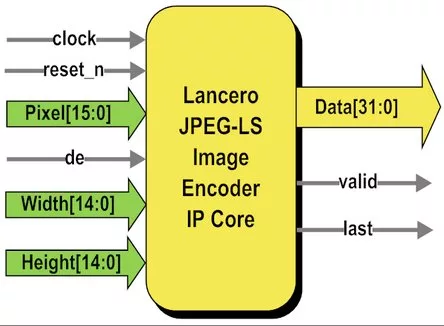

Block Diagram

Applications

- Medical (DICOM), military, space imaging

- Surveillance camera’s

- High-end film and photo scanners

- Satellite and space imaging

What’s Included?

- Encrypted Lancero JPEG-LS IP Core with pixel FIFO interface

- Altera Avalon Streaming bus wrapper

- Simulation Test Benches

- C bitstream identical model with cross validation against RTL

- Technical support

- Full SystemVerilog RTL source code can be licensed on request

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Video Processing IP core

Configurable Processors for Video Processing SOCs

FPGA-based video surveillance comes of age

Picking the right MPSoC-based video architecture: Part 1

Video encoding with low-cost FPGAs for multi-channel H.264 surveillance

Analysis: ARC's Configurable Video Subsystems

Frequently asked questions about Video Processing IP

What is JPEG-LS Lossless Image Encoder?

JPEG-LS Lossless Image Encoder is a Video Processing IP core from Microtronix Datacom Ltd. listed on Semi IP Hub.

How should engineers evaluate this Video Processing?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Processing IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.