The OT3135 is a flexible low power clock multiplier PLL function with a wide range of input and output frequencies, and is designed for TSMC 40nm, ULP CMOS processes.

Low Power Clock Multiplier PLL for 40nm TSMC ULP CMOS

Overview

Key Features

- Wide range M, P, and N integer dividers.

- 40MHz – 600MHz output frequency range.

- Input frequency range 1.4MHz – 32MHz.

- 15pS RMS cycle to cycle jitter.

- Lock-detect function.

- Optional bypass function.

- Level shifted IO.

- Well-defined, fast startup behavior.

- -40°C to 125°C temperature operation.

- Small area: 0.03mm2 in 40nm CMOS.

- 100µW typical power dissipation.

- 0.82-1.1V digital and analog supplies.

- Silicon proven.

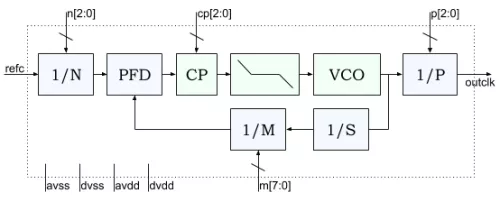

Block Diagram

Technical Specifications

Foundry, Node

152n, 180n CMOS

Maturity

Silicon proven

Availability

Now

TSMC

Silicon Proven:

40nm

LP

Related IPs

- 600MHz General Purpose Clock Multiplier PLL for 180n CMOS

- Ultra-Low Power Fractional-N digital PLL for IoT Applications in 40nm CMOS

- 8-bit <=25GSa/s High-speed Low power ADC in 16nm TSMC CMOS

- 25MHz to 200MHz Low Jitter Low Power PLL

- Ultra low Power 1.4GHz Frac-N PLL IP Core

- Low Power High Speed 1.2GHz Frac-N PLL IP Core