The world-leading hardware IP provider, Chips&Media, pre-released the multi-standard HW IP named WAVE517, targeting 4K ultra-high-definition (UHD), which is the first in the industry to support almost every codec standards for the UHD in the market, including the MPEG standard HEVC (High-Efficiency Video Coding) standard known as H.265, AVC/H.264, Google’s VP9, Chinese AVS2 and AOM's AV1 with optimized size and stable decoding performance.

The WAVE517 is architected for real-time decoding video capability of 4Kp60 content at 450MHz in HEVC/H.265, AVC/H.264, VP9, AVS2, and AV1 standards, and may achieve up to 8K resolution. Also, it’s cost-effective as it is architected to pick out and reuse sharable blocks from various codec standards and apply to the common blocks; in which the IP architecture becomes streamlined with minimum logics and memories fitting into small-sized SoCs.

In addition to its superior 4K60fps performance, the WAVE517 also provides maximum bandwidth efficiency and exceptionally low power consumption, which are today’s most demanding requirements across all connected devices. It employs frame buffer compression technology named CFrame which can save on average 50~80% bandwidth access to memory.

The WAVE517 is suitable for applications across various industry segments including ultra-high-definition televisions(UHDTVs), set-top boxes(STBs), VR·ARs, smartphones, tablets, data servers, and any others with super-high resolution.

HEVC/H.265, H.264, VP9, AV1 and AVS2 Multi format Decoder IP for 4K 60fps

Overview

Key Features

- Brief specification

- HEVC/H.265 Main/Main10 Profile @L5.1

- AV1 Main Profile @ L5.1

- VP9 Profile 0/ Profile 2 @L5.1

- AVC/H.264 BP/CBP/MP/HP/HP10 Profile @ L5.2

- AVS2 Main/Main10 Profile @L8.0.60

- Main performance

- 4K(3840x2160) 60fps @ 450MHz

- Max. resolution: 8192x4096

- System I/F

- A 32-bit APB bus and 128-bit AMBA3 AXI buses (w/additional Secondary AXI)

- Burst Write Back (BWB)

- Features

- Frame buffer compression (CFrame)

- Embedded Post-processing (w/Down-scaler)

- Low delay

- Low power consumption

- Latency tolerance

Benefits

- Multi-instance handling for multi-channel decoding

- Configurability for codec standard and customizable features

- 50~60% bandwidth saving while decoding process by reference frame compression

- Superior Error handling

- Supports property API SW

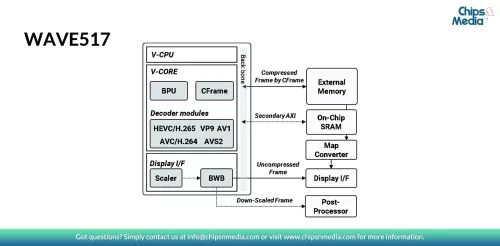

Block Diagram

Applications

- Mobile

- IP Cam / Surveillance

- Automotive

- Data Server

- DTV / D-STB

- IoT / Portable

- VR/AR

Deliverables

- RTL Source Code

- Programmer's Guide

- C Model User Guide

- Data Sheet / Verification Guide

- API Reference Manual

Technical Specifications

Foundry, Node

28nm, 16nm, 12nm and below

Availability

Available

Related IPs

- HEVC/H.265, H.264, VP9 and AVS2 Multi format Decoder IP for 4K 60fps

- HEVC/H.265, H.264 and AVS2 Multi format Decoder IP for 4K 60fps

- HEVC/H.265, H.264 Multi format Decoder IP for 4K 60fps

- HEVC/H.265, H.264 Multi format Encoder IP for 4K 60fps

- HEVC/H.265, H.264 Multi format Codec IP for 4K 60fps

- HEVC/H.265, H.264 Multi format Dual-core Codec IP for 8K 60fps