Silicon-verified, production-proven eFPGA for MCU/SoC/custom ASIC applications - optimized for edge and endpoint AI processing, military and automotive.

QuickLogic has been supplying eFPGA-based products for consumer, industrial and mission-critical applications for nearly three decades. Our eFPGA IP enables SoC designers the flexibility to easily program custom functions, hardware accelerators and security capability after an SoC has been manufactured.

eFPGA IP and FPGA Software Built on GLOBALFOUNDRIES 22FDX

Overview

Key Features

- High-performance architecture for low power applications

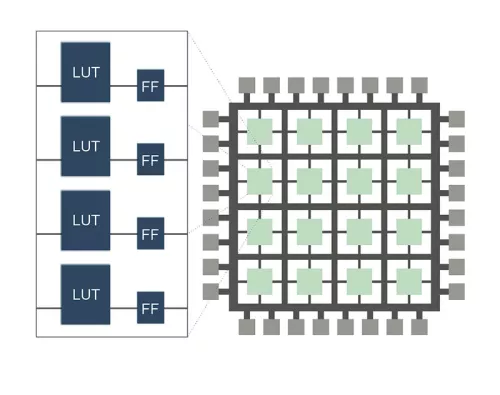

- Super Logic Cell (SLC) clusters 4 logic cells together with hierarchical routing networks for optimum performance and power consumption

- Each logic cell can be used as two separate 4-input LUTs or one 5-input LUT.

- Direct input selection to the register allows combinatorial and sequential logic to be used separately.

- Multiple outputs per logic cell are strategically selected to either feedback within the same SLC or to travel out to another SLC. A shared register clock, set, and reset signals for all four logic cells helps reduce routing congestion.

- Array sizes ranging from 8×8 SLC up to 64×64 SLCs

Benefits

- Expand addressable market of your SoC through on-chip reprogrammability

- Market test new features and functions before committing to hard gates or custom silicon

- Protect your ASIC by using the eFPGA as a reprogrammable isolation area for security or authentication IP

- Extends product longevity and hardware-based Continuous Integration (CI)

Block Diagram

Technical Specifications

Foundry, Node

GLOBALFOUNDRIES 22FDX

GLOBALFOUNDRIES

Pre-Silicon:

22nm

FDX

Related IPs

- eFPGA IP and FPGA Software Built on Samsung Foundry 28nm FDSOI

- 65nm/40nm Low Power eFPGA IP and Open Source FPGA Software

- Complete memory system supporting any combinations of SDR SDRAM, DDR, DDR2, Mobile SDR, FCRAM, Flash, EEPROM, SRAM and NAND Flash, all in one IP core

- High-performance 2D (sprite graphics) GPU IP combining high pixel processing capacity and minimum gate count.

- 2D (vector graphics) & 3D GPU IP A GPU IP combining 3D and 2D rendering features with high performance, low power consumption, and minimum CPU load

- MIPI C-PHY-D-PHY Combo PHY IP on TSMC 28nm HPC+