Implements a CAN bus controller that performs serial communication according to the CAN 2.0, CAN FD, and CAN XL specifications. It supports the original Bosch protocol and ISO specifications as defined in ISO 11898—including time-triggered operation (TTCAN) as specified in ISO 19898-4—and is also optimized to support the popular AUTOSAR and SAE J1939 specifications.

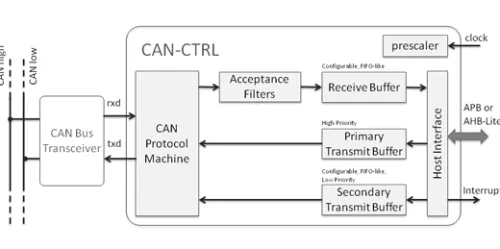

The CAN protocol uses a multi-master bus configuration for the transfer of frames between nodes of the network and manages error handling with no burden on the host processor. The core enables the user to set up economic and reliable links between various components. It appears as a memory-mapped I/O device to the host processor, which accesses the CAN core to control the transmission or reception of frames.

The CAN core is easy to use and integrate, featuring programmable interrupts, data and baud rates; a configurable number of independently programmable acceptance filters. ; and a generic processor interface or optionally an AMBA APB, or AHB-Lite interface. It implements a flexible buffering scheme, allowing fine-tuning of the core size to satisfy the requirements of each specific application.

The number of receive buffers is synthesis-time configurable. Two types of transmit buffers are implemented: a high-priority primary transmit buffer (PTB) and a lower-priority secondary transmit buffer (STB). The PTB can store one message, while the number of included buffer slots for the STB is synthesis-time configurable 0 to 16 slots.

The core implements functionality similar to the Philips SJA1000 working with its PeliCAN mode extensions, providing error analysis, diagnosis, system maintenance and optimization features.

The CAN core is extensively verified and proven in multiple production designs.

CAN 2.0, CAN FD & CAN-XL Bus Controller

Overview

Key Features

- CAN Specifications Support

- CAN 2.0 & CAN-FD (ISO 11898-1.2015, plus earlier ISO and Bosch specifications)

- CAN XL (CiA 610-1 specification)

- TTCAN (ISO 11898-4 level 1)

- Optimized for AUTOSAR and SAE J1939

- Enhanced Functionality

- Error Analysis features enabling diagnostics, system maintenance, and system optimization

- Last error type

- Arbitration lost position

- Error Warning Limit

- Listen-Only Mode enables CAN bus traffic analysis and automatic bit-rate detection

- Loop back mode for self-testing

- Time-stamping support, compliant to CiA's 603 specification

- Optional ECC memories support

- Flexible Message Buffering and Filtering

- Configurable number of receive buffers

- One high-priority transmit buffer

- Configurable number of lower-priority transmit buffers

- FIFO or priority mode for transmit buffers

- Configurable number of independently programmable 29-bit acceptance filters, 1 to 16

- Easy to Use and Integrate

- Programmable data rate up to 1 Mbit/s with CAN 2.0 and several Mbit/s with CAN FD option

- Programmable baud rate prescaler: 1 up to 1/256

- Single Shot Transmission Mode for lower software overhead and fast reloading of transmit buffer

- Programmable interrupt sources

- Generic 8-bit host-controller interface and optional 32-bit AMBA-APB or 32-bit AHB-Lite

- Safety Features (optional)

- SO-26262 ASIL-B Ready: Implements ECC for SRAM and spatial redundancy for inner logic protection

- ISO-26262 ASIL-C on request

- Zero Risk

- Compatible with any CAN2.0 transceiver (PHY) that supports ISO-11898, and various CAN-FD PHYs from NXP, MicroChip, OnSemi, Infineon, etc.

- Multiple times production proven

- Efficient and Portable Design

- Available in RTL, and portable to ASIC and FPGA technologies

Block Diagram

Applications

- The CAN-CTRL core can be integrated in devices that use CAN or higher-layer, CAN-based communication protocols. In addition to traditional automotive applications, such devices are used in industrial (e.g. the CANopen and DeviceNet protocols), aviation (e,g. the ARINC-825 and CANaerospace protocols), marine (e.g. the NMEA 2000 protocol) and other applications.

Deliverables

- The core includes everything required for successful implementation:

- VHDL or Verilog RTL source code

- Post-synthesis EDIF (netlist licenses)

- Testbenches

- Behavioral tests

- Post-synthesis verification

- Simulation scripts

- Synthesis scripts

- Linux driver

- Documentation

Technical Specifications

Maturity

Production Proven

Availability

Now