R-Stratus-LPRR is THE new generation of cache controller for MCU applications whenever the application program is stored in a Non Volatile Memories (NVM) like eFlash or EEPROM.

R-Stratus LPRR provides the twofold advantage of speed improvement and of power consumption minimization.

AMBA 3 AHB-lite compliant.

R-Stratus LPRR includes a Retention Ready feature to allow fast CPU wake-up from deep sleep mode.

Cache controller including Retention Ready feature for fast CPU wake-up time and very low power consumption

Overview

Key Features

- TSMC Soft IP qualification (IP9000)

- Straightforward connection

- Support of AHB-Lite interfaces to ensure fast and smooth integration in any MCU subsystem without need for any bridge

- External TAG and Cache memories to improve portability across a wide range of process technologies

- Standard interface for TAG and Cache memories

- Performance optimization (optional)

- Highly user configurable cache controller (associativity, cache line size, critical word first...) simplified with Smartvision for checking in simulation that the configuration is optimal for achieving the best speed and power consumption

- Improvement of processing power

- Apparent frequency is accelerated up to 11 times

- Zero wait state for cache hit

- Critical word first to reduce the number of cycles in case of miss

- First cache controller optimized for low power

- Architecture designed to minimize the number of accesses to TAG and cache RAM and NVM

- Runtime programmable cache line size and associativity

- Up to 14 times less power consuming!

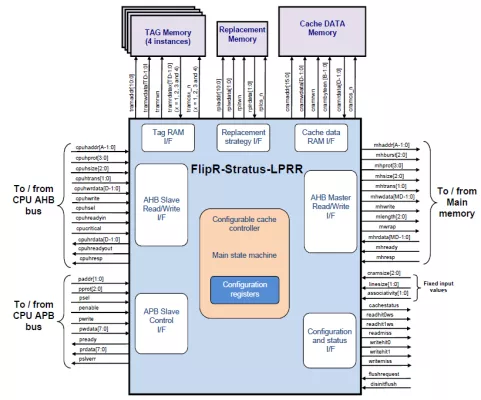

Block Diagram

Technical Specifications

Related IPs

- Cache controller including Retention Ready feature for fast CPU wake-up time and very low power consumption

- 2D (vector graphics) & 3D GPU IP A GPU IP combining 3D and 2D rendering features with high performance, low power consumption, and minimum CPU load

- Cache controller for fast NVM memories access and very low power consumption

- ARC EM7D DSP Enhanced 32-bit processor core with caches, ARCv2DSP ISA, for low power embedded DSP ap

- 2-cluster Power Consumption & Performance Efficiency Enhanced Series6XT 3D/2D/Compute GPU including OpenGL ES 3.0, DX10_0 Feature Level and OpenCL Support , 10-bit YUV, YUV framebuffer, ASTC

- 4-cluster Power Consumption & Performance Efficiency Enhanced Series6XT 3D/2D/Compute GPU including OpenGL ES 3.0, DX10_0 Feature Level and OpenCL Support, 10-bit YUV, YUV framebuffer, ASTC