The AXI to APB Bridge translates an AXI bus transaction (read or write) to an APB bus transaction. This is accomplished via two state machines – one governing the AXI transactions, and one governing APB transactions.

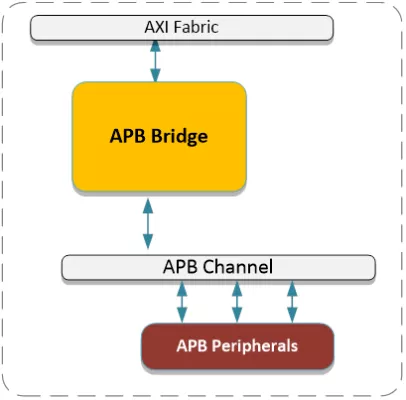

The AXI to APB Bridge acts as an AXI Slave, and an APB Master in an AXI/APB subsystem. Typically, the AXI to APB Bridge has its AXI interface connected to a Slave port on an AXI Channel/Interconnect module, and its APB interface connected to the Master port on an APB Channel module.

AXI to APB Bus Bridge

Overview

Key Features

- Translates AMBA® AXI transactions to APB transactions

- Low latency

- Low Gate Count

- Supports APB 2.0 and APB 3.0 Signaling

- Independent ACLK, PCLK pseudo-synchronous clocks

- AMBA® AXI-4 Compatible

- Multiple AXI Channels

- Off the shelf core supports 4 Masters and 8 Slaves

- Arbitration is done at each slave

- Other configurations are available

Block Diagram

Deliverables

- Verilog Source

- Complete Test Environment

- AHB Bus Functional Model

- C-Sample Code

Technical Specifications

Maturity

Silicon Proven

Availability

Now