The OT3130 is a flexible clock multiplier PLL function with a wide range of input and output frequencies and is designed for TSMC 152nm, CMOS processes.

Single use license from $17K.

800MHz General Purpose PLL

Overview

Key Features

- Wide range M, P integer dividers.

- 50MHz – 800MHz output frequency range.

- Compare frequency range 8MHz – 32MHz.

- 15pS RMS cycle to cycle jitter at 800MHz.

- Lock-detect function.

- Bypass function.

- Well-defined, fast startup behavior.

- -40°C to 140°C temperature operation.

- Available divider selection program.

- Small area: 0.03mm2 in 0.152µ CMOS.

- 3mW typical power dissipation.

- 1.8V digital and analog supplies.

- 0.152µ CMOS process compatibility.

- Silicon proven many times.

- Mature architecture.

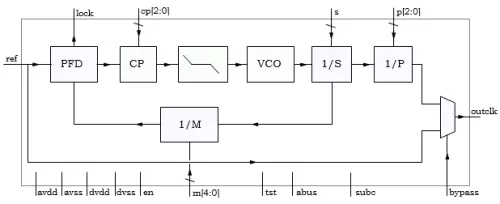

Block Diagram

Applications

- Crystal frequency to device internal clock multiplication.

- Communication cores.

- Bus Interface cores.

Deliverables

- Verilog model.

- Metal outline.

- Spice netlist for LVS.

- Design review spice files.

- GDS.

- Timing files.

- Integration notes.

- Production test notes.

Technical Specifications

Foundry, Node

152n, 180n CMOS

Maturity

Silicon

Availability

Now

SMIC

Silicon Proven:

180nm

G

TSMC

In Production:

180nm

G

,

180nm

LP

Pre-Silicon: 150nm G

Silicon Proven: 180nm G , 180nm LP

Pre-Silicon: 150nm G

Silicon Proven: 180nm G , 180nm LP