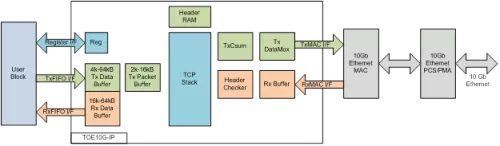

10GbE TCP Off-loading Engine(TOE10G-IP) IP core is the epochal solution implemented without CPU. Generally, TCP processing is so complicated that expensive high-end CPU is required. TOE10G-IP built by pure hardwired logic can take place of such extra CPU for TCP protocol management. This IP product includes reference design for Intel FPGA. It helps you to reduce development time.

DesignGateway provide demo file for Intel FPGA boards. You can evaluate TOE10G-IP

10GbE TCP Offloading Engine

Overview

Key Features

- 10GbE TCP/IP stack implementation

- Support IPv4 protocol

- Support one port connection

- Support both Server and Client mode (Passive/Active open and close)

- Support Jumbo frame

- Transmit/Receive buffer size, programmable on HDL for optimized resource

- Simple data interface by standard FIFO interface

- Simple control interface by standard register interface

- One clock domain interface by fixed 156.25 MHz clock frequency

- Super low-latency DG 10G EMAC-IP for TOE10G-IP core (Option)

- Support Multi-session (8 Sessions Reference design is available)

- Provide free evaluation demo file for FPGA Development Kits (1 hour time limited)

- Reference design is included in IP core product

Block Diagram