The 10/25/40/100G MAC IP core is a Low-Latency Ethernet MAC with a latency of 44.8ns in 2749 LUTs for 10Gbit/s and 20.5ns in 2680 LUTs for 25Gbit/s. When combined with the Low-Latency 10/25GPCS, the full packet round trip time for 10Gbit/s is ( MAC Input -> Wire -> MAC Output ) 153.8ns in 5153 LUTs; 25Gbit/s ( MAC Input -> Wire -> MAC Output ) is 128ns in 7930 LUTs.

The IEEE 802.3by compliant 10/25/40/100G MAC/PCS was designed in house at Chevin Technology, to provide an easy path to the integration of protocols such as TCP/IP and UDP protocols in your FPGA, whilst using minimal FPGA resources. The 10/25/40/100G MAC simplifies the synthesis of ultra-fast Duplex 25Gbit/s Ethernet for FPGAs.

10/25/40/100G MAC/PCS Ethernet IP Core

Overview

Key Features

- Ultra-Low Latency: 160 nanosecond packet Round Trip Time (RTT) in 7 Sreies, Kintex & Virtex® UltraScale™

- Cut-through mode operation for minimum latency

- Deficit Idle Count / Programmable IFG– Minimize IFG

- Designed to IEEE 802.3-2008; IEEE 802.3ae-2002 specifications, 10GBASE-R

- Fault Management, BER monitoring

- Small Footprint; Combined 5100 LUTs & 2 Block RAMs

- Statistics counters for frames and bytes sent/received, size bins, FCS errors, broadcast

- Reference design available for Alpha Data's ADM-PCIE-KU3, ADM-PCIE-8V3, ADM-PCIE-9V3 boards.

Benefits

- Significantly increase the efficiency and rate of data transfer by providing lowest possible latency.

- Straightforward integration of 10Gbit/s Ethernet connectivity in Xilinx 7 Series, Kintex & Virtex® UltraScale™ FPGAs.

- Cut-through mode operation minimizes latency

- Store-and-forward feature allows for minimum application load

- Competitively priced licenses available to suit the size and requirements of each project.

- Customers can evaluate the RTT for themselves using a bitfile on Chevin Technology’s eco-system partner Alpha Data’s ADM-PCIE-KU3, ADM-PCIE-8V3, ADM-PCIE-9V3 boards.

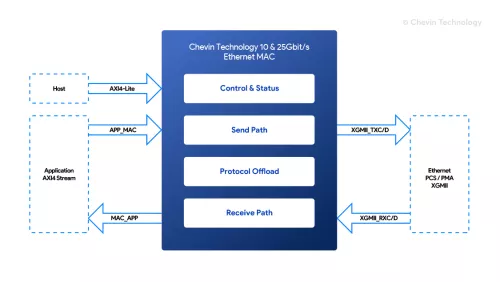

Block Diagram

Applications

- Trade execution & monitoring

- Data Storage & Capture systems

- HPC / Big Data systems

- Signal processing systems

- Data Mining

Deliverables

- Encrypted RTL/VHDL source code for simulation

- Encrypted compiled netlist

- Datasheet & User Guide to assist integration

- Simulation Test bench

- Build scripts for Vivado

- Support for integration into FPGA

Technical Specifications

Availability

Now

Related IPs

- Complete memory system supporting any combinations of SDR SDRAM, DDR, DDR2, Mobile SDR, FCRAM, Flash, EEPROM, SRAM and NAND Flash, all in one IP core

- BCH Encoder/Decoder IP Core

- 10/25/40/100G Ethernet PCS/PMA

- DDR-I/II/III CONTROLLER IP CORE

- High-performance, low-power 2D composition IP core for embedded devices

- Vector Graphics IP core supporting OpenVG1.1 subset