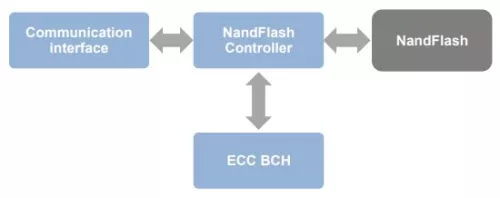

Nand Flash write cycles are limited. An ECC detects and corrects failed operations, increasing the lifetime of the Nand Flash memory. For Nand Flash-based data storage, using an ECC is mandatory to ensuring data validity. The ECC is based on the BCH algorithm. The Encoder/Decoder is full-featured with ease-of-use in FPGA and SoC designs.

The BCH Encoder/Decoder is fully configurable, allowing to it reach the best latency or the smallest footprint. Customizable parameters include: Chien Search algorithm, Galois Field, and data path. The IP-Maker BCH Encoder/Decoder IP Core is delivered in Verilog RTL that can be implemented in an ASIC or FPGA. It is fully tested with test bench models and hardware tested with FPGAs. The package includes Verilog RTL code, technical documentation, and a complete test environment.