The USB 2.0 PHY IP provides designers with the industry's best combination of low area and low power with support for USB Type-C connectivity in leading process technologies from 65-nm to 14/16-nm FinFET. The USB 2.0 PHY IP products include the USB 2.0 femtoPHYs, USB 2.0 picoPHYs, USB 2.0 nanoPHYs, and USB 2.0 HSIC-LPM PHYs.

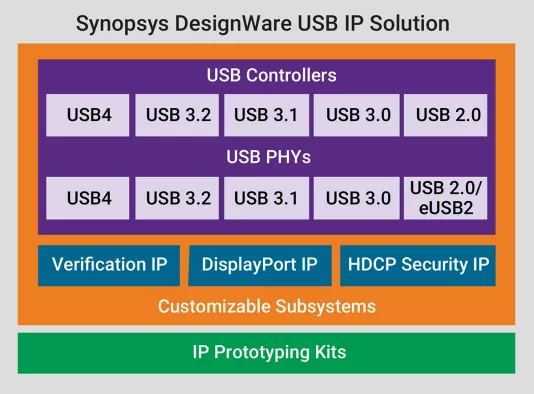

The USB IP is the most certified USB IP solution in the industry. With over 3,000 design wins and over one billion silicon-proven units shipped, the vendors's complete USB IP solution, consisting of digital controllers, PHY and Verification IP, enables designers to lower integration risk and speed time-to-market.