The Silicon Creations Multi-Rate SerDes (Serializer/Deserializer) includes all high-speed analog functions for a single channel serializer and deserializer and is optimized for low power operation within a data raterange of 125Mb/s to 1.25Gb/s. A 10b input and output datapath simplifies the design of link layers created from RTL using regular standard cells and regular synthesis, place, and route flows. Excellent supply noise immunity in the CDR and TX PLLs makes the SerDes ideal for use in noisy mixed signals SoC environments.

SGMII SerDes

Overview

Key Features

- Separate PLLs for Tx and Rx

- Compatible with arbitrary numbers of parallel lanes

- 10bit datapath for TX and RX

- Flexible driver and receiver circuits compatible with LVDS, 4b current programming

- Trimmable on-die termination ensures excellent signal integrity

- High-speed loop-back path simplifies production testing

- 50 mW total power consumption @ 1.25Gb/s

- 10,000 ppm RX frequency tolerance

- Optional half-rate quadrature output clock

- Fractional-N TXPLL control

- 3 auxiliary post divide outputs from TX

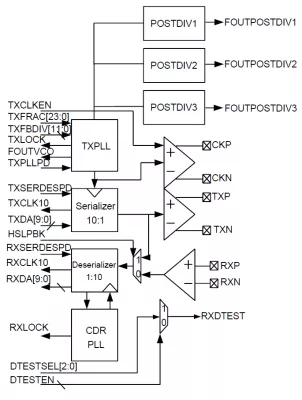

Block Diagram

Deliverables

- GDSII

- CDL Netlist (MG Calibre Compatible)

- Functional Verilog Model

- Liberty timing models (.lib)

- LEF

- Application Note with integration and production test guidelines

Technical Specifications

Foundry, Node

TSMC 65nm - 180nm; Global Foundries 28nm - 65nm; SMIC 65nm; Renesas 90nm

Maturity

Mass Production

Availability

Available Now

TSMC

In Production:

65nm

LP

,

90nm

G