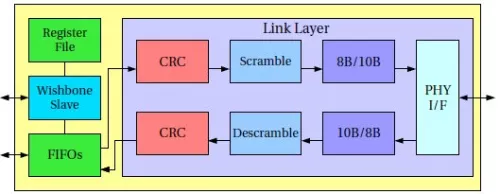

The Serial ATA Host IP Core provides an interface to high-speed serial link replacements for the parallel ATA attachment of mass storage devices. The serial link employed is a high-speed differential layer that utilizes Gigabit technology and 8b/10b encoding.

5th generation, Silicon proven IP Core.

Serial ATA Host Controller (1.5, 3.0, 6.0 Gb/s) 5th Generation

Overview

Key Features

- High Throughput: <b>531</b> MBytes/sec Read, <b>505</b> MBytes/sec Write

- Low Latency: <b>66K IOPS</b> Read, <b>67K IOPS</b> Write (4k blocks)

- Connects to SAPIS compliant serial ATA Phy

- Asynchronous, unrestricted SoC clock, independent of PHY clock

- Includes Xilinx Transceiver based PHY

- Fully compliant to SATA V3.0 <b>COMPLIANCE CERTIFIED</b>

- NCQ

- Port Multipliers

- Port Selector

- FIS based switching

- Supports Gen 1 (1.5 Gbps), Gen 2 (3.0 Gbps) and Gen 3 (6.0 Gbps)

- <b>AXI Light</b> interface for register access

- <b>AXI Stream</b> Interface and for data transfers

- Full support for PIO, DMA and FPDMA transfers

- 128 byte (32 double word) data FIFO (optional 256 byte)

- Implements the shadow register block and the serial ATA status and control registers

- Parallel ATA legacy software compatibility

- 48-bit address feature set supported

- 8b/10b coding and decoding

- CONT and data scramblers to reduce EMI

- CRC generation and checking

- Auto inserted HOLD primitives

- Power management support (partial and slumber)

- DMA Support

- Descriptor Based Command Processing

- Unlimited command list size

- Many configuration options

- ucLinux Drivers

Benefits

- High Performance

- AXI Interface

- Flexible

- Compact

- Cost-effective

- Many Shipping Products

Block Diagram

Applications

- Embedded Application

- ucLinux

- Data Recorder

Deliverables

- Verilog Source Code

- Test Bench

- Sample Synthesis scripts

- Documentation

- Reference Resign

- ucLinux Drivers

Technical Specifications

Foundry, Node

any

Maturity

production

Availability

now