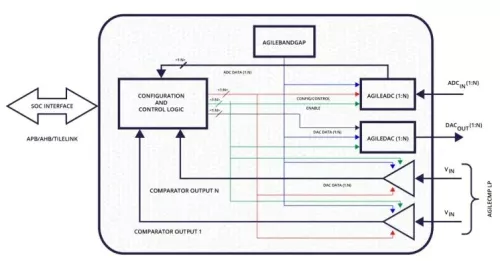

The agileSensorIF Subsystem is an efficient and highly integrated sensor interface for SoCs/ASICs. Featuring multiple Analog-to-Digital converters (agileADC), Digital-to-Analog converter (agileDAC), low-power programmable analog comparators (agileCMP_LP), and an associated reference generator (agileREF). The agileSensorIF Subsystem enables easy interaction with the analog world.

The components within the subsystem can be customized to suit a variety of applications. This includes selecting the number of agileADC, agileDAC, and agileCMP_LP blocks, as well as their bit depth and sample rate. This allows the agileSensorIF subsystem to be perfectly tailored to your exact needs and use case.

Status monitors provide real-time feedback on the current state of the subsystem, ensuring optimal system performance.

The monitoring of process, voltage and temperature variations are critical to optimize power and performance for modern SoCs/ASICs, especially for advanced node and FinFET processes.

Agile Analog designs are based on tried and tested architectures to ensure reliability and functionality. Our design methodology is programmatic, systematic and repeatable leading to analog IP that is more verifiable, more robust and more reliable. Our methodology also allows us to quickly re-target our IP to different process options. We support all the major foundries including TSMC, GlobalFoundries, Samsung Foundry, Intel, and SMIC as well as other IC foundries and manufacturers. Please contact Agile Analog for further information.

Sensor Interface Subsystem

Overview

Key Features

- agileADC

- Resolution: up to 12-bits

- Sampling Rate (Fs)1: up to 64 MSPS

- SNR1: Typ 70 dB

- ENOB1: Typ 11.3 bits

- SFDR1: Typ 90 dBc

- INL: +/2 LSB

- DNL: +/-1 LSB

- Up to 16 input channels

- agileDAC

- Resolution: up to 12-bits

- Sampling Rate (Fs)1: up to 20 MSPS

- SNR1: Typ 70 dB

- INL: +/2 LSB

- DNL: +/-1 LSB

- agileCMP_LP

- Programmable Thresholds

- Active Current: 1.5uA (max)

- Detection Time: 2us (typical)

- Hysteresis: 20mV

- Threshold Step Size: 56.25mV

- Threshold Accuracy: 10mV

- agileSensorIF Subsystem

- Industry standard digital interface

- Fully integrated macro

- Standard AMBA APB interface

Block Diagram

Technical Specifications

GLOBALFOUNDRIES

Pre-Silicon:

12nm

,

14nm

,

14nm

LPE

,

14nm

LPP

,

20nm

LPM

,

22nm

,

22nm

FDX

,

28nm

,

28nm

FDSOI

,

28nm

HPP

,

28nm

LPH

,

28nm

SLP

,

32nm

,

40nm

LP

,

55nm

,

55nm

LPX

,

65nm

,

65nm

LP

,

65nm

LPe

,

90nm

,

90nm

LP

,

130nm

,

130nm

HP

,

130nm

LP

,

130nm

LV

,

180nm

,

180nm

LL

,

180nm

LL

,

180nm

LP

,

180nm

LP

Intel Foundry

Pre-Silicon:

16nm

SMIC

Pre-Silicon:

14nm

,

28nm

,

28nm

HK

,

28nm

HKC+

,

28nm

PS

,

40nm

LL

,

55nm

G

,

55nm

LL

,

65nm

LL

,

90nm

G

,

90nm

LL

,

110nm

G

,

130nm

EEPROM

,

130nm

G

,

130nm

LL

,

130nm

LV

,

150nm

G

,

150nm

LV

,

153nm

,

160nm

G

,

160nm

LL

,

180nm

EEPROM

,

180nm

G

,

180nm

LL

,

250nm

G

Samsung

Pre-Silicon:

4nm

,

5nm

,

7nm

,

8nm

,

10nm

,

11nm

,

14nm

,

28nm

FDS

,

28nm

LPH

,

28nm

LPP

TSMC

Pre-Silicon:

3nm

,

4nm

,

5nm

,

6nm

,

7nm

,

10nm

,

12nm

,

16nm

,

20nm

,

22nm

,

28nm

,

28nm

HP

,

28nm

HPC

,

28nm

HPCP

,

28nm

HPL

,

28nm

HPM

,

28nm

LP

,

40nm

G

,

40nm

LP

,

45nm

GS

,

45nm

LP

,

55nm

FL

,

55nm

G

,

55nm

GP

,

55nm

LP

,

55nm

NF

,

55nm

ULP

,

55nm

ULPEF

,

55nm

UP

,

65nm

G

,

65nm

GP

,

65nm

LP

,

80nm

,

80nm

GT

,

80nm

HS

,

85nm

,

90nm

FS

,

90nm

FT

,

90nm

G

,

90nm

GOD

,

90nm

GT

,

90nm

LP

,

90nm

zzz

,

110nm

G

,

110nm

HV

,

110nm

LVP

,

130nm

,

130nm

BCD

,

130nm

BCD+

,

130nm

G

,

130nm

LP

,

130nm

LV

,

130nm

LVOD

,

150nm

G

,

150nm

LV

,

160nm

G

,

160nm

LP

,

180nm

,

180nm

E

,

180nm

ELL

,

180nm

FG

,

180nm

G

,

180nm

LP

,

180nm

LV

,

180nm

ULL

Tower

Pre-Silicon:

130nm

,

180nm

,

180nm

,

180nm

,

500nm

UMC

Pre-Silicon:

14nm

,

22nm

,

28nm

,

28nm

HLP

,

28nm

HPC

,

28nm

HPM

,

28nm

LP

,

40nm

,

40nm

LP

,

55nm

,

65nm

LL

,

65nm

LP

,

65nm

SP

,

80nm

,

90nm

G

,

90nm

LL

,

90nm

SP

,

110nm

,

130nm

,

150nm

,

162nm

Related IPs

- MIPI-I3C Combo Host and Target interface controller IP for Sensor and Peripheral connection

- USB 2.0 Hi-Speed OTG Controller Subsystem w/AHB Interface Supporting HSIC (config. as Device only or Full Speed only)

- Sensor & Control IP Subsystem

- PSI5 IP Core Controller for Peripheral Sensor Interface 5 Communication

- Pre-verified Interface IP Subsystems reduce design risk and accelerate time-to-market

- PCI Master/Target Interface Core