The Chevin Technology SATA-HC IP block simplifies the integration of high capacity SSDs utilizing SATA I/II/III at 1.5/3/6Gbit/s data rates using Xilinx FPGAs.

Combined low-latency and high throughput is achieved by accessing the SSD directly from FPGA logic with no external circuitry. The lower protocol layers Phy/Link/Transport are implemented in an all-RTL solution, which minimizes access time by providing the shortest possible path between SSD and application.

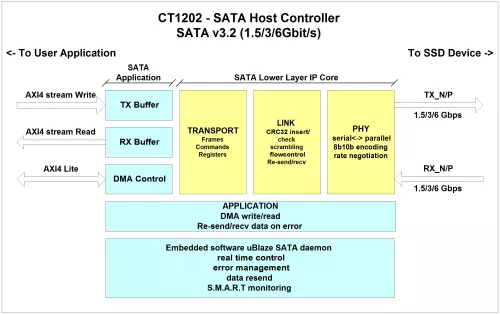

SATA 3.0 Host Controller

Overview

Key Features

- Designed to SATA v3.0 (6Gbps)

- Low Latency, SATA commands <1us

- High Throughput read/write @ 500MByte/s

- Small Footprint 5200 LUTs (lower layers)

- PHY/LINK/Trans/App layers in RTL

- DMA management SW in embedded CPU

- Host operating system not required

- S.M.A.R.T data collection

- Fault management, BER monitoring

- Detailed traffic analysis & statistics collection

- Client Interface, 32bit write/read streaming @ 37.5/75/150MHz (1.5/3/6 Gbps)

Benefits

- Integrated solution provides highest possible Megabytes per second.

- Sustained throughput enables consistent and predictable high performance.

Block Diagram

Applications

- Trade execution & monitoring

- Data Storage & Capture systems

- HPC / Big Data systems

- Signal processing systems

- Data Mining

Deliverables

- RTL VHDL source code

- Encrypted compiled netlist

- Datasheet & User Guide to assist integration

- Reference Design on Xilinx KC705 development board

- Simulation Test bench

- Build scripts for ISE/Vivado

- Support for integration into FPGA

Technical Specifications

Availability

Now