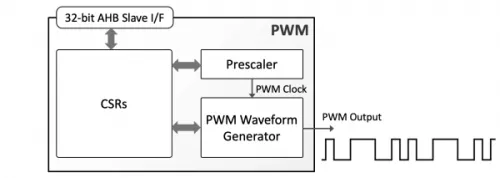

The PWM IP core implements a compact and highly flexible Pulse Width Modulator. The core generates a repeated pattern of pulse trains of run-time configurable period and duty cycle. Those pulse trains can be used in a wide variety of applications including but not limited to motor control and LED dimming. They can also be filtered with a lowpass filter to implement Digital to Analog Converters (DAC).

The core is designed for ease of use and integration and adheres to the industry's best-standards coding and verification practices. It provides access to its control and status registers via a 32-bit AMBA™ AHB or Wishbone slave port. APB, AXI4-Lite, or other interfaces can be made available on request. Technology mapping, timing closure, and scan insertion are trouble-free, as the core contains no multi-cycle or false paths and uses only rising-edge-triggered D-type flip-flops, and no tri-states.

Pulse Width Modulator

Overview

Key Features

- Advanced PWM Features

- Run-time programmable PWM pattern

- Limits long high or low times

- Essential for efficient DAC implementations

- Fine control of PWM period

- A 16-bit register value defines the length of the PWM period in terms of PWM clock cycles

- PWM clock derived using a fractional prescaler with 16-bit denominator and 16-bit numerator

- Updated PWM parameters applied either immediately or on the next PWM period.

- Interfaces

- 32-bit AHB or Wishbone Slave for CSR access

- APB or AXI4-Lite interface available on request

Block Diagram

Deliverables

- Verilog RTL source code or targeted FPGA netlist

- Integration Test-Bench

- Simulation & synthesis scripts

- Comprehensive user documentation