Power-On-Reset Samsung

Overview

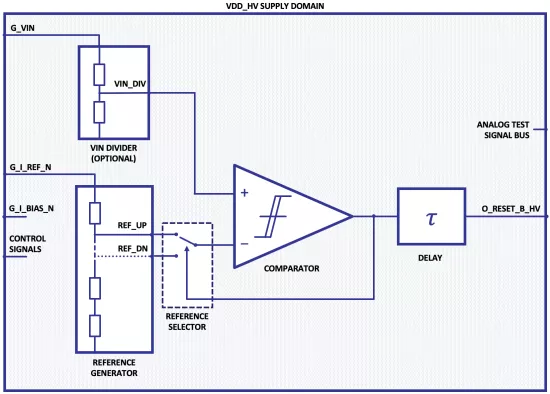

The agilePOR GP is a power-on-reset circuit. Based on a traditional architecture, it allows for programmable thresholds for normal and low power modes, programmable delays and includes hysteresis to avoid false resets in noisy environments.

Key Features

- Start-up Time: max 10us

- Configurable Threshold

- Programmable Delay

- Uses Hysteresis to avoid false resets in noisy environments

- Current Consumption: typ 100nA

- Customizable design for simple SoC integration

- Silicon Area – Please contact Agile Analog

Benefits

- Hysteresis

- - Avoids false resets due to noisy environments

- Configurable thresholds

- - Both upper and lower thresholds are programmable

- - Microprocessor held in reset during voltage rail ramp-up and during brown-out conditions

Block Diagram

Applications

- Combine with agileVGlitch and agileLDO to create a self contained voltage attack sensor sub-system.

Deliverables

- Datasheet

- Testing and Integration Guide

- Verilog Models

- Floorplan (LEF)

- Timing models (LIB)

- Netlist (CDL)

- Layout (GDS)

- Physical Verification Report

- Design Report

Technical Specifications

Foundry, Node

Samsung

Maturity

Available on request

Availability

Now

Samsung

Pre-Silicon:

4nm

,

5nm

,

7nm

,

8nm

,

10nm

,

11nm

,

14nm

,

28nm

FDS

,

28nm

LPH

,

28nm

LPP