The Qualitas' 8nm PCIe PHY IP consists of hardmacro PMA and softmacro PCS compliant to PCIe Base 4.0 specification. This IP offers a cost-effective and low-power solution using 8nm FinFet CMOS technology. It includes all ESD I/Os and bump pads, and supports extensive built-in self test features such as loopback and scan.

PCIe 4.0 PHY on 8nm

Overview

Key Features

- 8nm low power enhanced (LN08PP) CMOS device technology

- 1.8V±5%, 0.85V±5% dual power supply

- Compliant to PCIe Base 4.0 and PIPE 4.4.1 specification

- Support Gen1, Gen2, Gen3 and Gen4

- Channel Configuration for Data Lanes

- Common (CMN) and 1, 2 or 4 Data Lanes

- Support the following transmitter pre-emphasis levels

- - 3.5/-6dB for Gen1 and Gen2

- 3-tap FIR with resolution of 1/36 for Gen3 and Gen4

- Support CTLE and 5-tap DFE for channel equalization in receiver

- Support adaptive channel equalization

- 100MHz reference clock is required (Support differential input buffer)

- Built-in self test feature capable of generating and checking PRBS patterns

- Compatible PCS is supported in softmacro form

Benefits

- Low power consumption and small area

- Support 1-, 2- and 4- lane configurations

- Automatic built-in self-test (Loopback)

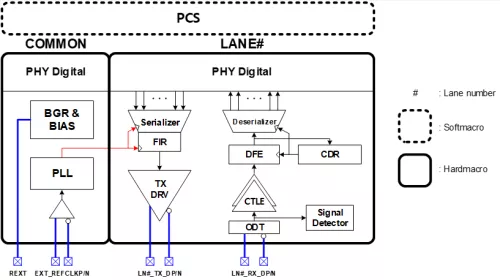

Block Diagram

Applications

- Mobile, Automotive, Storage, AI accelerator and Chip-to-chip interconnect

Deliverables

- FE-Common: MODEL, TWRAP, TB, LEF, LIBERTY, IPXACT, ATPG, PCS RTL, SDC, SIPI

- BE-Common: CIR, GDS, DRC, LVS, DFM

- DOC-Common: DataSheet, UserGuide, TestGuide

Technical Specifications

Foundry, Node

Samsung Foundry 8LPU

Maturity

Silicon Proven

Availability

Now

Samsung

Silicon Proven:

8nm

Related IPs

- PCI Express 4.0 PHY

- PCIe 4.0 PHY on 5nm

- PCIe 4.0 LP PHY, TSMC N7RF x1, North/South (vertical) poly orientation

- PCIe 4.0 PHY, TSMC16FFC x1, North/South (vertical) poly orientation

- PCIe 4.0 PHY, TSMC16FFC x2, North/South (vertical) poly orientation

- PCIe 4.0 PHY, TSMC16FFC x4, North/South (vertical) poly orientation