Low Power Successive-Approximation ADC 37.5 MS/s 12-Bit

Overview

This IP describes a general purpose Analog to Digital Converter (ADC) for low-power applications. The converter is a charge-redistribution successive-approximation type converter, and it is suitable to operate in a time-interleaved ADC to enable higher sample-rates. As an example, this ADC is applied in a 2.5 GS/s ADC system. The key feature of this ADC is its low power consumption. Next to this, the full-scale range is programmable and its area is small. The IP product described in the datasheet is silicon proven. The 2.5 GS/s ADC system in which this ADC is applied fulfills all mass-production consumer electronics requirements.

Key Features

- sample-rate up to 37.5 MS/s

- scalable full-scale input range 0.4-0.6 VPP,SE

- low power consumption 6.3 mW

- differential mode

- 62 dB SNR

- 70 dB SFDR (incl THD)

- 12 bits, 10 ENOB

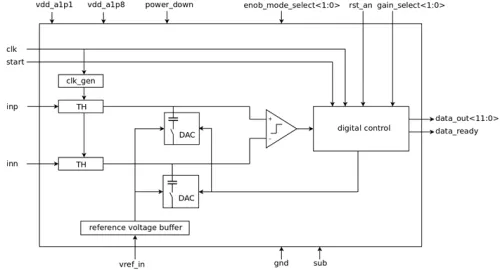

Block Diagram

Applications

- Multi-mode digital receivers

- Cable modems

- Video digitizing and CCD imaging

- Portable instrumentation

- Medical imaging

Technical Specifications

Foundry, Node

GlobalFoundries 40nm LP CMOS

Maturity

Ready for mass-production

Availability

Now

GLOBALFOUNDRIES

In Production:

40nm

LP

Silicon Proven: 40nm LP

Silicon Proven: 40nm LP

Related IPs

- 12-bit 1-channel up to 1 MSPS low power SAR ADC

- 8-bit <=25GSa/s High-speed Low power ADC in 16nm TSMC CMOS

- 12-bit ultra-low power single-ended SAR ADC

- High Performance / Low Power Microcontroller Core

- Ultra low power C-programmable DSP core

- Highest code density, Low Power 32-bit Processor with optional DSP