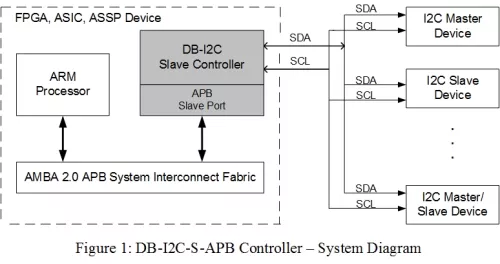

The Digital Blocks DB-I2C-S-APB Controller IP Core interfaces an ARM, MIPS, PowerPC, ARC or other high performance microprocessor via the AMBA 2.0 APB System Interconnect Fabric to an I2C Bus. The I2C is a two-wire bidirectional interface standard (SCL is Clock, SDA is Data) for transfer of bytes of information between two or more compliant I2C devices.

The DB-I2C-S-APB is a Slave I2C Controller that controls the Transmit or Receive of data to or from external Master I2C devices. Figure 1 depicts the system view of the DB-I2C-S-APB Controller IP Core embedded within an integrated circuit device.

I2C Slave Controller w/FIFO (APB Bus)

Overview

Key Features

- I2C Slave Controller - Implements Slave-only protocol for smaller VLSI footprint, for applications requiring Slave–Receiver and Slave–Transmitter capability

- SCL Clock only for low power, low noise applications requiring configuration & management of User Registers

- 7- or 10-bit addressing, General Call, SCL Low Wait States

- Supports five I2C bus speeds:

- Standard mode (100 Kb/s)

- Fast mode (400 Kb/s)

- Fast mode plus (1 Mbit/s)

- Ultra fast mode (5 Mbit/s)

- Hs-mode (3.4 Mbit/s)

- Compliance with I2C specifications:

- Philips – The I2C-Bus Specification, Version 2.1, January 2000

- NXP Rev .5 October 9, 2012

- Fully-synchronous, synthesizable Verilog RTL core. Easy integration into FPGA or ASIC design flows.

Block Diagram

Deliverables

- Verilog RTL Source or technology-specific netlist.

- Comprehensive testbench suite with expected results.

- Synthesis scripts.

- Installation & Implementation Guide.

- Technical Reference Manual.

Technical Specifications

Foundry, Node

Chartered, Global Foundries, Intel, LSI. OKI, Silterra, SMIC, STMicroelectronics, Tower, TMSC, UMC

Maturity

Successful in Customer Implementations

Availability

Immediately

Related IPs

- I2C Master / Slave Controller w/FIFO (APB Bus)

- I2C Slave Controller w/FIFO (APB or AHB or AHB-Lite or AXI-Lite Bus)

- I2C Master Controller w/FIFO (APB Bus)

- I2C Master / Slave Controller w/FIFO (AXI & AXI-Lite Bus)

- I2C Master / Slave Controller w/FIFO (AHB & AHB-Lite Bus)

- SPI Master / Slave Controller w/FIFO (APB Bus)