The agileDSCL is a compact digital standard cell library customisable for specific foundries and processes, and optimised for low-power, ultra-low-leakage, high-density or high-speed applications.

It provides a selection of standard cells with functionalities essential to implement digital designs, with additional power management library to support the implementation of low-power designs.

Please contact Agile Analog to discuss specialised libraries

Agile Analog designs are based on tried and tested architectures to ensure reliability and functionality. Our design methodology is programmatic, systematic and repeatable leading to analog IP that is more verifiable, more robust and more reliable.

Our methodology also allows us to quickly re-target our IP to different process options. We support all the major foundries including TSMC, GlobalFoundries, Samsung Foundry and SMIC as well as other IC foundries and Manufacturers. Please contact Agile Analog for further information.

Digital Cell Library Samsung

Overview

Key Features

- Compact standard cell library targeting a wide range of foundries and processes

- Customised for low-power, ultra-low-leakage, high density or high-speed applications with choices of:

- Multiple VT and channel length

- Thick-Oxide based cells

- Various track heights

- Power Management library for low-power designs

- Timing models for customisable range of PVT

- High Quality library with class leading validation and models compatible with industry standard tools

Benefits

- Optimised for PPA targets / DFM

- DFM-optimised

- Customisation

- Agile Analog’s COMPOSATM tool enables efficient creation of libraries for specific foundries, processes, and cell architectures.

- Possibility to generate models at customised PVT corners

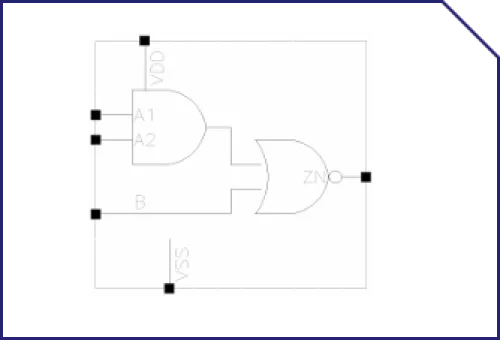

Block Diagram

Applications

- IoT, Security, Automotive, AI, SoCs, ASICs

Deliverables

- Datasheet

- Testing and Integration Guide

- Verilog Models

- Floorplan (LEF)

- Timing models (LIB)

- Netlist (CDL)

- Layout (GDS)

- Physical Verification Report

- Design Report

Technical Specifications

Foundry, Node

Samsung

Samsung

Pre-Silicon:

4nm

,

5nm

,

7nm

,

8nm

,

10nm

,

11nm

,

14nm

,

28nm

FDS

,

28nm

LPH

,

28nm

LPP

Related IPs

- Digital Cell Library Intel

- 28nm Wirebond IO library with dynamically switchable 1.8V/ 3.3V GPIO, 5V I2C open-drain, 1.8V & 3.3V analog, OTP program cell, and HDMI & LVDS protection macros - featured across a variety of metal stack and pad configuration options

- A 130nm Wirebond IO library with 3.3V GPIO, LVDS TX & RX, 3.3V I2C open-drain, analog cell and OTP program cell

- A 180nm Flip-Chip IO library with 1.2-1.8V GPIO, 1.8V & 5V analog/RF, 20-36V ultra-low leakage low-cap HV analog and OTP program cell

- Standard Cell Library in TSMC (12nm~180nm)

- 6 track High Density standard cell library at TSMC 180nm