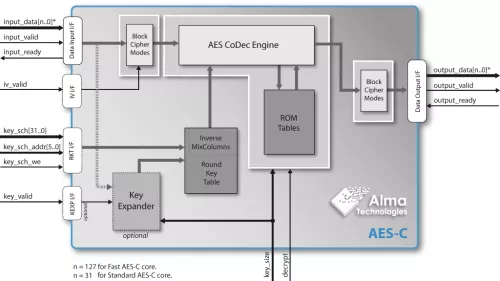

The AES-C core from Alma Technologies implements the FIPS-197 Advanced Encryption Standard. It can be programmed to encrypt or decrypt 128-bit blocks of data, using 128-, 192-, or 256-bit cipher-key. An included configurable wrapper surrounds the AES-C core and implements its fixed Block-Cipher mode of operation. This configurable wrapper supports the ECB, CBC, CFB, OFB and CTR Block-Cipher modes.

The AES-C core is available in two variations, the standard AES32-C and the fast AES128-C: AES32-C has a 32-bit internal datapath, while the AES128-C uses 128-bit datapath. The AES32-C variation is more compact in size, but offers a lower throughput than the AES128-C. The AES32-C needs 44/52/60 clock cycles to encrypt or decrypt an input block using 128/192/256-bit cipher-key, respectively, while only 11/13/15 clock cycles are required for the same by the AES128-C core.

During each step of the encryption or decryption processing the core requires a previously calculated Round Key Value, derived from the cipher-key using a key expansion algorithm. These Round Key Values must be stored to the internal Round Key Table, from which the core retrieves the appropriate one for each processing step. Alternatively, instead of directly programming the Round Key Values to the Round Key Table, an optional Key Expander module can be provided. This module automatically calculates the Round Key Values and fills the internal Round Key Table according to the cipher-key given to the core.

The AES-C core is equipped with easy-to-use fully stallable interfaces for both input and output. These are designed to permit the user application to pause the produced output data stream when it is not able to receive data, or to pause the input stream towards the core according to data arrival rate.

AES Encryption & Decryption with Fixed Block-Cipher Mode

Overview

Key Features

- Compliant, High-Performance and Standalone Operation

- Fully compliant to the Advanced Encryption Standard (AES) (FIPS PUB 197)

- Block-Cipher mode configurable during synthesis: ECB, CBC, CFB, OFB, CTR

- Run-time programmable encrypt or decrypt

- Run-time programmable cipher-key size: 128-, 192-, 256-bit

- Includes Round Key Table for storage of Round Key values

- Optional Key Expansion module for automatic generation of the Round Key values

- AES32-C: Processes each 128-bit block in 44/52/60 clock cycles for 128/192/256-bit cipher-key respectively

- AES128-C: Processes each 128-bit block in 11/13/15 clock cycles for 128/192/256-bit cipher-key respectively

- High-speed, flow controllable, streaming I/O data interfaces

- Trouble-Free Technology Map and Implementation

- Fully portable, self-contained RTL source code

- Strictly positive edge triggered design

- D-type only Flip-Flops

- Fully synchronous operation

- No special timing constraints required

- No false paths

- No multi-cycle paths

- Clear text VHDL or Verilog RTL source for ASIC designs, or pre-synthesized & verified Netlist for Altera, Lattice, Microsemi and Xilinx FPGA and SoC devices

- Release Notes, Design Specification and Integration Manual documents

- Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

- Self checking testbench environment, including sample BAM generated test cases

- Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts

Block Diagram

Deliverables

Technical Specifications

Maturity

Silicon Proven

Availability

NOW

Related IPs

- AES Encryption & Decryption with Programmable Block-Cipher Mode

- AES data encryption and decryption

- AES Encryption and Decryption

- Cryptographic library for encryption and decryption of Advanced Encryption Standard (AES) in ECB, CBC, OFB, CTR and GCM modes

- AES Authenticated Encryption Accelerator with DPA or with DPA and FIA

- Inline cipher engine for PCIe, CXL, NVMe, 5G FlexE link integrity and data encryption (IDE) using AES GCM mode