8-10 bit DAC SMIC

Overview

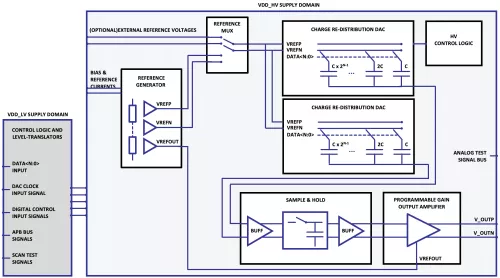

The agileDAC GP is a digital-to-analog converter that uses a traditional capacitive DAC architecture. The agileDAC uses its own internal reference voltage. The architecture can achieve up to 10-bit resolution at sample rates up to 16 Msps.

Key Features

- Resolution: 8b/10b,

- Sampling Rate (Fs): up to 16Msps

- Output Signal Bandwidth: Typ Fs/2

- Guaranteed monotonic

- SFDR1: Typ -60dBc

- INL: Max2 ±4LSB

- DNL: Max2 ±2LSB

- Conversion Time: Typ 2 cycles

- Quiescent current3 (Iq):Typ 250uA

- Customizable design for simple SoC integration

- Integrated Calibration Mode

- Silicon Area – Please contact Agile Analog

Benefits

- DFT/DFM

- - AMBA-APB Interface to simply test and operation

- - Built-in Trim and Calibration to facilitate process and/or manufacturing offsets to be adjusted

Block Diagram

Applications

- IoT, Security, Automotive, AI, SoCs, ASICs

Deliverables

- Datasheet

- Testing and Integration Guide

- Verilog Models

- Floorplan (LEF)

- Timing models (LIB)

- Netlist (CDL)

- Layout (GDS)

- Physical Verification Report

- Design Report

Technical Specifications

Foundry, Node

SMIC

Maturity

Available on request

Availability

Now

SMIC

Pre-Silicon:

14nm

,

28nm

,

28nm

HK

,

28nm

HKC+

,

28nm

PS

,

40nm

LL

,

55nm

G

,

55nm

LL

,

65nm

LL

,

90nm

G

,

90nm

LL

,

110nm

G

,

130nm

EEPROM

,

130nm

G

,

130nm

LL

,

130nm

LV

,

150nm

G

,

150nm

LV

,

153nm

,

160nm

G

,

160nm

LL

,

180nm

EEPROM

,

180nm

G

,

180nm

LL

,

250nm

G