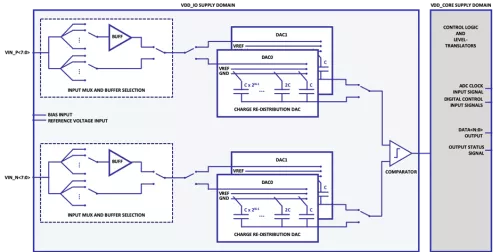

The agileADC analog-to-digital converter is a traditional Charge-Redistribution SAR ADC that is referenced to VDD, VSS. The architecture can achieve up to 10-bit resolution at sample rates up to 20 MSps. It includes an eight-channel input multiplexor. Some inputs will be buffered inside the ADC, whereas others will bypass the buffer and be connected directly to the ADC to provide full rail-to-rail capability..

8-10 bit SAR ADC SMIC

Overview

Key Features

- Resolution: 8b, 10b

- Sampling Rate (Fs): 1 Msps to 20Msps

- Input Signal Bandwidth: Fs/2

- SINAD1: Typ 54dB

- SFDR1: Typ -60dBc

- CMRR2: min 65dB

- PSSR1: Typ 30dB

- Monotonic and no missing codes

- Customisable design for simple SoC integration

- Integrated Calibration Mode

- Silicon Area – Please contact Agile Analog

Benefits

- DFT/DFM

- - AMBA-APB Interface to simply test and operation

- - Incorporated Trim and Calibration to facilitate process and/or manufacturing offsets to be adjusted

- - Built-in test mode

- Configurable Inputs

- - Up to 8 input channels

- - Buffer or unbuffered

- - Differential or Single-ended-

- Rail-to-Rail input

Block Diagram

Applications

- IoT, Security, Automotive, AI, SoCs, ASICs

Deliverables

- Datasheet

- Testing and Integration Guide

- Verilog Models

- Floorplan (LEF)

- Timing models (LIB)

- Netlist (CDL)

- Layout (GDS)

- Physical Verification Report

- Design Report

Technical Specifications

Foundry, Node

SMIC

Maturity

Available on request

Availability

Now

SMIC

Pre-Silicon:

28nm

,

28nm

HK

,

28nm

HKC+

,

28nm

PS

,

40nm

LL

,

55nm

G

,

55nm

LL

,

65nm

LL

,

90nm

G

,

90nm

LL

,

110nm

G

,

130nm

EEPROM

,

130nm

G

,

130nm

LL

,

130nm

LV

,

150nm

G

,

150nm

LV

,

160nm

G

,

160nm

LL

,

180nm

EEPROM

,

180nm

G

,

180nm

LL