The multi-lane Multi-Protocol 32G PHY IP is part of a high-performance multi-rate transceiver portfolio for high-end networking and cloud computing applications. The PHY is small in area and provides a low active and standby power solution that supports multiple electrical standards, including PCI Express (PCIe) 5.0, 1G to 400G Ethernet, Cache Coherent Interconnect for Accelerators (CCIX), Compute Express Link (CXL), SATA, and other industry-standard interconnect protocols Using leading-edge design, analysis, simulation, and measurement techniques, the multi-protocol 32G PHY delivers signal integrity and jitter performance that exceeds the standards electrical specifications.

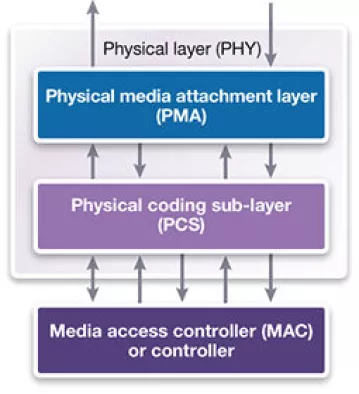

The configurable transmitter and receiver equalizers along with Continuous Calibration and Adaptation (CCA) enable designers to control and optimize signal integrity and performance across voltage and temperature variations. The PHY provides advanced power management features for both standby and active power. The BERT and internal eye monitor provide on-chip testability and visibility into channel performance. The PHY integrates seamlessly with the Synopsys Physical Coding Sublayer (PCS) and Media Access Control (MAC) to reduce design time and to help designers achieve first-pass silicon success.