The SDCRDAC24bHBW is a 24-bit sigma-delta charge-redistribution digital-to-analog converter (DAC). It is designed to have high absolute accuracy, low noise and low power consumption, and it is robust against temperature variations. This makes the DAC ideally suited for high-performance audio as well as demanding control applications in a wide variety of environments.

The product is based on the SDCRDAC24b, but this version is not radiation hardened. Instead, the SDCRDAC24bHBW has increased bandwidth, increased temperature stability and lower power consumption.

This product is silicon-verified.

24-bit Sigma Delta Charge-Redistribution DAC (High bandwidth)

Overview

Key Features

- Noise floor: <-139dBV (10uHz - 1Hz)

- Noise floor: -138dBV (1Hz - 50Hz)

- Noise floor: -112dBV (20Hz - 20kHz)

- Input sample rate: 0-3MS/s

- Total out-of-band noise: < -60dB, without filtering

- Low latency (down to 9 cock cycles): Ideal for closed loop applications

- Wide common mode range

- Quasi-differential outputs

- Outputs suitable for both current-mode and voltage-mode operation

- Total power consumption: 950 uW (fclk=4MHz; power scales linearly with fclk)

- Gain stability vs temperature: <2ppm/K

- Low offset: <3uV

- No code dependent loading of Vref

- Technology: UMC 0.18 um CMOS

- Silicon-verified

- Design is scalable with regard to area and performance

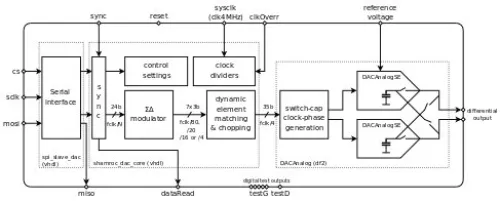

Block Diagram

Applications

- High-precision control systems

- Automatic test equipment

- Gain and offset adjustment/calibration

- Programmable voltage and current sources

- Process and servo control

- High-quality audio

- Active noise reduction systems

Technical Specifications

Foundry, Node

UMC 0.18 um CMOS

Maturity

silicon-verified

Availability

Now

UMC

Silicon Proven:

180nm

Related IPs

- 24-bit Sigma Delta Stereo Audio Ulter low area silicon provenin 28nm DAC

- Low power 24bit few Ksps sigma Delta silicon proven DAC IP Core

- 24-Bit High resolution sigma-delta charge-redistribution DAC

- High Accuracy, low-noise sigma delta DAC

- 24-bit 128Ksps Analog front end (AFE) having sigma delta ADC for Energy Metering application

- 24-bit 14.4Ksps Analog front end (AFE) having sigma delta ADC for Industrial process control and sensors