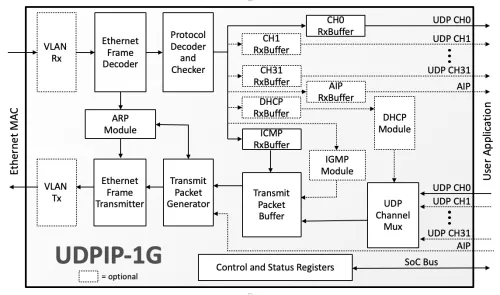

Implements a UDP/IP hardware protocol stack that enables high-speed communication over a LAN or a point-to-point connection. Designed for standalone operation, the core is ideal for offloading the host processor from the demanding task of UDP/IP encapsulation and enables media streaming with speeds up to 1Gbps even in processor-less SoC designs.

Trouble-free network operation is ensured through run-time programmability of all the required network parameters (local, destination and gateway IP addresses; UDP ports; and MAC address etc.). The core implements the Address Resolution Protocol (ARP), which is critical for multiple access networks, and the Echo Request and Reply Messages (“ping”) of the Internet Control Message Protocol (ICMP) widely used to test network connectivity. It can use a static IP address or automatically request and acquire an IP address from a Dynamic Host Configuration Server (DHCP) server. Furthermore, the core supports 801.1Q tagging, and is suitable for operation in a Virtual LAN.

The core is easy to integrate in systems with or without a host processor. Packet data can be read/written to the core via dedicated AMBA® AXI4-stream or Avalon®-ST interfaces, while registers are accessible via an AXI4-Lite, or AHB or Avalon-MM slave interface. Bridges to other interface protocols can be made available up on request. The core is Ethernet MAC-independent, but can be made available pre-integrated with an Intel, Xilinx, or other third-party eMAC core.

This core can be mapped to any any Intel, Lattice, MicroSemi, or Xilinx programmable device, or to any ASIC technology, provided sufficient silicon resources are available. Please contact CAST Sales to get accurate characterization data for your specific implementation requirements.

UDP/IP Hardware Protocol Stack

Overview

Key Features

- Complete UDP/IP Hardware Stack

- 10/100/1000 Ethernet

- IPv4 support without packet fragmentation

- Jumbo and Super Jumbo Frames

- Transmit and Receive

- ARP with Cache

- ICMP (Ping Reply)

- IGMP v3 (Multicast)

- UDP/IP Unicast, and Multicast

- UDP Port Filtering

- UDP/IP Checksums generation and validation, and optional Ethernet CRC validation

- VLAN (IEEE 802.1Q) support

- 1 to 32 UDP transmit. and 1 to 32 UDP receive channels

- Ethernet Framing processing for non-UDP user-provided packets

- Optional DHCP client

- Trouble-Free Network Operation

- Run time programmable network parameters:

- Local MAC address, Local IP address, Gateway IP address, and IP subnet mask

- Per channel: Destination IP address, Source and Destination and filtered UDP ports, multicast enable/disable and receive group

- ARP support for operation in networks with Dynamic IP allocation

- Easy SoC Integration

- 32- or 64-bit streaming capable using Avalon-ST or AXI4-Stream

- Control/Status interface with optional 32-bit AHB, AXI, Avalon-MM or Wishbone SoC buses

- Separate clock domains for packet processing and control/data interfaces

- Configurable buffer sizes

- Rich interrupt support for system events

- Optionally available pre-integrated with:

- Intel, Xilinx, or other third-party eMAC cores

- CAST Image and Video compression cores

Block Diagram

Applications

- Video, image and audio streaming or broadcasting over Ethernet, in devices such as IP cameras compatible to the GigE Vision, ONVIF, or PSIA standards, VOIP and smart phones. Also high-frequency trading systems, high-speed communication between LAN nodes, device monitoring, and control over IP networks.

Deliverables

- The core is available in synthesizable RTL and FPGA netlist forms, and includes everything required for successful implementation, including a sophisticated self-checking testbench, simulation scripts, test vectors, and expected results, synthesis scripts and comprehensive user documentation.

Technical Specifications

Maturity

Production Proven

Availability

Now