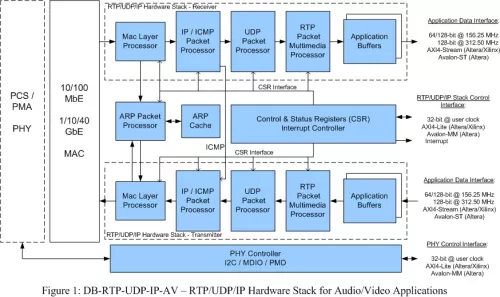

The Digital Blocks DB-RTP-UDP-IP-AV IP Core is a RTP/UDP/IP Protocol Hardware Stack with MAC Layer Pre- & Post-Processors and an ARP Packet Processor targeting low latency, full off-load from a processor, of Audio/Video Packet Processing. The DB-RTP-UDP-IP-AV is a Verilog SoC IP Core targeting Xilinx/Altera/Lattice FPGAs and ASIC/ASSP devices.

RTP / UDP / IP Hardware Stack for Audio / Video Application

Overview

Key Features

- 10/100 Mb & 1/10/40 Gb wire-line performance with ultra-low latency

- Address Resolution Protocol (ARP) Packet Processor (client/server)with 4-16 entry ARP cache

- Internet Protocol (IP) Packet Processor:

- Support for both IPv4 and IPv6 protocols

- IP & ICMP (Internet Control Message Protocol) Protocol

- Host IP address filter, IP header checksum check & generator, user selectable Maximum Transmission Unit (MTU), Unicast & Multicast Packet support

- User Datagram Protocol (UDP)Packet Processor:

- Support for up to 256 UDP Ports

- UDP header checksum check & generator

- Real-time Transport Protocol (RTP) Packet Processor

- Encapsulates/Decapsulates H.264/NAL streams to RTP packets

- Compliant with RFC 3894 and RFC 6184

- High Speed Data Interface to user Host Application

- PHY Controller – control interface to user Host Application

Block Diagram

Deliverables

- Verilog RTL Source or technology-specific netlist.

- Comprehensive testbench suite with expected results.

- Synthesis scripts.

- Installation & Implementation Guide.

- Technical Reference Manual.

Technical Specifications

Foundry, Node

IBM, LSI, TMSC, UMC, Tower, GlobalFoundaries

Maturity

Successful in Company FPGA Kit Demo Reference Design, Customer Products

Availability

Immediately