Chips&Media CODAJ12V is a standalone and high-performance JPEG codec IP that can perform JPEG Baseline/Extended and MJPEG decoding and encoding.

Compliant with the Extended sequential DCT mode of ISO/IEC 10918-1 JPEG standard, the CODAJ12V can also support motion JPEG streams with varied color formats supporting resolutions up to 32K x 32K.

Its fully hardware-based architecture provides high performance and low power consumption, suitable for a variety of digital imaging applications.

On-the-fly pre- and post-image processing can also contribute to improving memory bandwidth efficiencies.

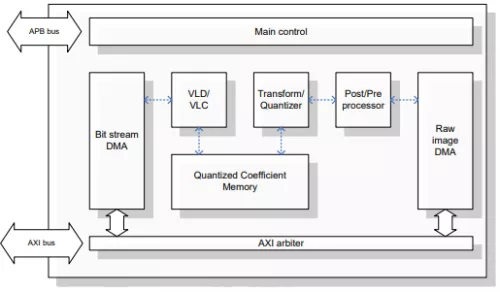

CODAJ12V is designed for reliability and easy integration, which is connected to the system via a 32-bit AMBA3 APB bus for system control and via a 64-bit AMBA3 AXI bus for data throughput.

Hardware 8-bit/12-bit JPEG Codec IP

Overview

Key Features

- Decoding/Encoding Tools

- Support Extended Sequential ISO/IEC 10918-1 JPEG compliance

- Support one or three color components

- Three components in a scan (interleaved only)

- 8-bit and 12-bit samples for each component

- Support 4:2:0, 4:2:2, 4:4:0, 4:4:4 and 4:0:0 color formats

- Max. six 8x8 blocks in one MCU

- Support NV12/NV16/NV24 (CbCr Interleaved), NV21/NV61/NV42 (CrCb Interleaved)

- Support from 16 x 16 to 32K x 32K (32,768 x 32,768) image size

- Packed mode is supported

- 12-bit PPM format is supported

- Value-added Features

- Partial mode for encoding and decoding

- On-the-fly rotator/mirror

- ROI(Region of Interest) for decoding

- On-the-fly downsampler for decoding

- Color format converting for decoding

- Performance

- Decode up to 290M pix/s for 4:2:0 color format

- Encode up to 290M pix/s for 4:2:0 color format

- Operating clock frequency: 200MHz

- Ease of integration

- AMBA 32-bit APB (w/ PREADY) interface for communication with a host processor

- AMBA 64-bit AXI interface for the external memory

Benefits

- Standard Compliance

- Compliant with Extended Sequential ISO/IEC10918-1 JPEG standard

- Compliant with Motion JPEG

- Advanced Hardware Architecture

- High-performance decoding up to 290M pix/sec (4:2:0 format)

- High-speed encoding up to 290M pix/sec (4:2:0 format)

- Unified Encoder & Decoder Design

- Very small silicon area footprint

- Ultra-low power consumption

- Comprehensive Integration Support

- Easy system integration with AMBA APB/AXI bus

- Complete verification platforms supported

Block Diagram

Applications

- Mobile phones

- Digital cameras

- Digital camcorders

- Medical imaging systems

- Video conference systems

- Surveillance systems

- Scanners and printers

- Digital photo frames

- Automotive systems

Deliverables

- RTL source code

- RTL testbench

- Datasheet

- Verification/C-model Guide

- API Reference Manual

- Programmer's Guide

Technical Specifications

Availability

Available

Related IPs

- High Performance 8bit/12bit JPEG CODEC

- Baseline JPEG Codec with optional Constant Bitrate Motion JPEG Video Rate Control

- High Speed Low Power JPEG Codec IP Core

- ITU-T G729A Voice Codec Hardware Accelerator

- JPEG Codec 4K(YUV422) 96fps@200MHz,

- Lossless JPEG Codec Full HD(YUV422) 24fps@100MHz. (1Sample/clk)