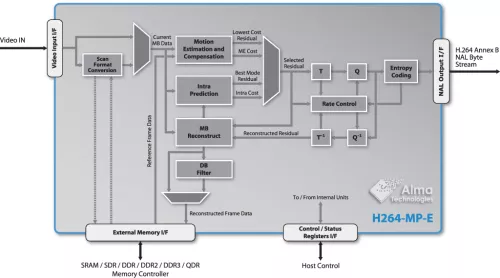

The H264-MP-E core from Alma Technologies is an advanced H.264 hardware encoder that conforms to the Main Profile of the ITU-T H.264 standard. The core is also available in ALL-Intra (H264-MPI-E) and Light Motion Estimation engine (H264-MP-E-LME) encoding configurations and supports the real time encoding of video streams up to Profile Level 5.2. Encoding in the Constrained Baseline Profile is also supported.

The encoder accepts the uncompressed video data in planar, interleaved, or macroblock scan format. It outputs standalone, standard compliant, Annex B NAL byte stream. No post processing on the output stream, other than (for example) stroring, muxing or transmitting, is required. The output NAL byte stream can be decoded, as is, by any ITU-T H.264 compliant decoder that satisfies the Level requirements of the stream and conforms to the Main, or higher, ITU-T H.264 Profile.

H264-MP-E requires minimal host intervention as it only needs to be programmed once per video sequence. Once programmed, it can encode an arbitrary number of video frames without needing any CPU or other type of support by the host system.

The H264-MP-E core implements a simple and flexible, requests based, external memory interface with independent read and write data paths. This makes the H264-MP-E independent of memory type, supporting for example operation with SRAM, SDRAM, DDR, DDR2 and DDR3 types of memory. The encoder is designed to be tolerant to memory delays and latencies, which may be present on shared memory system architectures.

The H264-MP-E core is designed with simple, fully controllable and FIFO-like, streaming input and output interfaces. Being carefully designed, rigorously verified and silicon-proven, the H264-MP-E is a reliable and easy-to-use and integrate IP.

H.264 Main Profile Encoder

Overview

Key Features

- Standard Compliant and Standalone Operation

- Full compliance to the ITU-T H.264 Main Profile specification

- Constrained Baseline Profile conformance also supported

- Multi-format 4:2:0 YCbCr digital video input

- ITU-T H.264 Annex B compliant NAL byte stream output

- Profile Level up to 5.2

- No host CPU assisted, standalone operation

- Advanced H264 Implementation

- 16 video lines algorthmic encoding latency

- True H.264 compression efficiency and perceptually optimized Image Quality

- Advanced Motion Estimation

- Full search

- Variable block size

- Full, half and quarter pixel

- Up to 4 motion vectors per macroblock

- Advanced Intra prediction

- All 4 Intra 16x16 prediction modes

- All 4 Intra Chroma prediction modes

- All 9 Intra 4x4 prediction modes

- Intra in P (all prediction modes are always examined)

- High throughput implementation: Sustained 2.5 clock cycles per pixel worst case processing rate

- CABAC entropy coding

- CQP - VBR encoding mode

- CBR encoding mode

- Fully customizable through runtime encoding settings

- HRD CPB compliant CBR NAL output

- Intra Refresh encoding mode available for sub-frame contribution to the end-to-end latency

- On-the-fly bitrate changes supported

- Error resilient encoding options

- Multiple slices per frame encoding option

- Motion vectors can be optionally constrained within slice boundaries

- Deblocking filter can be optionally constrained within slice boundaries

- Smooth System Integration

- Full abstraction of the internal implementation details and the H.264 complexity from the top level I/O and its operation

- Simple, microcontroller like, programming interface

- High-speed, flow controllable, streaming I/O data interfaces

- Simple and FIFO like

- Avalon-ST compliant (ready latency 0)

- AXI4-Stream compliant

- Low requirements in external memory bandwidth

- Flexible external memory interface

- Independent of external memory type

- Tolerant to latencies

- Allows for shared memory access

- Can optionally operate on independent clock domain

- Trouble-Free Technology Map and Implementation

- Fully portable, self-contained RTL source code

- Strictly positive edge triggered design

- D-type only Flip-Flops

- Safe CDC transfers when using more than one clock domain

- No special timing constraints required

- No false or multi-cycle paths within the same clock domain

- No CDC transfers that need to be constrained (all CDC paths can be excluded)

- Clear text VHDL or Verilog RTL source for ASIC designs, or pre-synthesized & verified Netlist for Altera, Lattice, Microsemi and Xilinx FPGA and SoC devices

- Release Notes, Design Specification and Integration Manual documents

- Bit Accurate Model (BAM) and test vector generation binaries, including sample scripts

- Self checking testbench environment, including sample BAM generated test cases

- Simulation and sample Synthesis (for ASICs) or Place & Route (for FPGAs) scripts

Block Diagram

Deliverables

Technical Specifications

Maturity

Silicon Proven

Availability

NOW