ZipAccel-C is a custom hardware implementation of a lossless data compression engine that complies with the Deflate, GZIP, and ZLIB compression standards.

The core receives uncompressed input files and produces compressed files. No post processing of the compressed files is required, as the core encapsulates the compressed data payload with the proper headers and footers. Input files can be segmented, and segments from different files can be interleaved at the core’s input.

The core’s flexible architecture enables fine-tuning of its compression efficiency, throughput, and latency to match the requirements of the end application. Throughputs in excess of 100 Gbps are feasible even in low-cost FPGAs, and latency can be as small as a few tens of clock cycles.

ZipAccel-C offers compression efficiency practically equivalent to today’s popular deflate-based software applications. Analyzing processing speed versus compression efficiency to achieve the best trade off for a specific system is facilitated by the included software model, and by support from our team of data compression experts.

ZipAccel-C has been designed for ease of use and integration. It operates on a standalone basis, off-loading the host CPU from the demanding task of data compression, and optionally from the task of encrypting the compressed stream. Streaming data interfaces and optional AMBA bus interfaces ease SoC integration.

Technology mapping is straightforward, as the design is scan-ready, microcode-free, and uses easily replaceable, generic memory models. Memory blocks can optionally support Error Correction Codes (ECC) to simplify achievement of Enterprise Class reliability requirements. Furthermore, input file segmentation can limit the inter-file latency and helps users achieve Quality of Service (QoS) objectives. The core has been rigorously verified and production proven in numerous commercial products.

GZIP/ZLIB/Deflate Data Compression Core

Overview

Key Features

- Compression Standards

- Deflate (RFC-1951)

- ZLIB (RFC-1950)

- GZIP (RFC-1952)

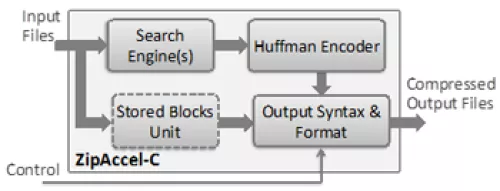

- Deflate Features

- LZ77 with configurable block and search widow size

- Static and Dynamic Huffman

- Optional Stored Deflate Blocks

- Dynamic Mode Selection

- Flexible Architecture

- Fine-tune Throughput, Compression Efficiency, and Latency to match application requirements

- More than 100Gbps with one core instance, scalable to meet any throughput requirement

- Compression efficiency can be on par with Unix/Linux max compression option (gzip -9)

- Silicon requirements start from 20k gates

- Under 15 clock cycles (Static Huffman)

- Configuration Options

- Search Engine and Huffman Encoder blocks Architecture

- History Search Window Size (up to 32KB)

- Deflate Block Size

- Deflate Blocks Support

- Parallel Processing Level

- Easy to Use and Integrate

- Processor-free, standalone operation

- Streaming-capable interfaces and optional AMBA bus wrappers

- Large file segmentation enables meeting QoS objectives

- Microcode-free, scan-ready design

- Optional ECC memories, necessary for Enterprise-Class RASM

- Optionally integrated with AES-XTS and AES-GCM encryption companion cores

- Fine-tune Throughput, Compression Efficiency, and Latency to match application requirements

Block Diagram

Applications

- The ZipAccel-C core is ideal for increasing the bandwidth of optical, wired or wireless data communication links, and for increasing the capacity of data storage in a wide range of devices such as networking interface/routing/storage equipment, data servers, or SSD drives. The core can also help reduce the power consumption and bandwidth of centralized memories (e.g. DDR) or interfaces (e.g. Ethernet, Wi-Fi) in a wide range of SoC designs.

Deliverables

- HDL RTL source code (ASICs) or post-synthesis EDIF netlist (FPGAs)

- Sophisticated Test Environment

- Simulation scripts, test vectors and expected results

- Synthesis script

- Comprehensive user documentation

Technical Specifications

Maturity

Production Proven

Availability

Now

Related IPs

- Data Compression

- JPEG XS compression IP core for HD - Max fps: 60 - Color sampling: 4:2:2 / 4:0:0

- CCSDS 122.0-B-1 Encoder - Lossless and Lossy Image Data Compression with up to 16 bits Pixel Dynamic Range

- High Throughput and Low Latency Data Compression Engine

- 4K TicoRAW Encoder / Decoder for RAW CFA sensor data compression

- 8K TicoRAW Encoder / Decoder for RAW CFA sensor data compression