Implements an Ethernet Media Access Controller compatible with the 10/100 Mbps IEEE 802.3 and 1Gbps IEEE 802.3-2002 specifications. The controller provides half- or full-duplex operation, supports jumbo frames, and optionally provides a reach set of statistics counters enabling station management.

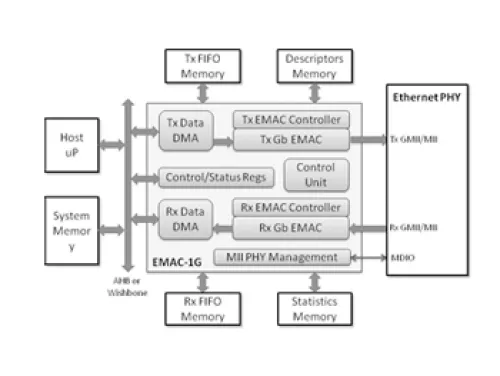

A host processor can control the operation of the core via a slave interface that provides access to its control and status registers. The EMAC-1G features two master ports for data transfers, one for transmit and one for receive. The two DMA engines use buffer descriptors to automatically transfer data from local FIFOs to an external shared memory. The core supports 32-bit AMBA/AHB or Wishbone SoC buses; other bus interfaces are available on request.

Integration with an Ethernet PHY is straightforward, as the controller core supports the Media Independent Interface (MII) and the Gigabit Media Independent Interface (GMII) physical layer interface standards.

The EMAC-1G is production proven in ASIC and FPGA technologies.

Gigabit Ethernet Media Access Controller

Overview

Key Features

- Data Link Layer

- Programmable 10/100 or 1000 Mbps operation

- IEEE 802.3-2002 specification with preamble, start-of-frame delimiter (SFD), and CRC generation and checking

- Full- or half-duplex operation

- CSMA/CD procedures for half duplex

- Flow control for full duplex

- Jumbo frames

- Flexible address filtering

- Extensive statistics counters

- Detection of too long or too short packets, with programmable length limits

- PHY Interfaces

- Media Independent Interface (MII) for 10/100Mbps

- Gigabit Media Independent Interface (GMII) for 1Gbps

- MDIO interface for PHY configuration and management

- Host Interface

- AMBA/AHB or Wishbone 32-bit slave for status and control

- One interrupt line per Tx and Rx.

- Clock switch control port (10/100 or 1000 Mbps)

- DMA controller

- AMBA/AHB or Wishbone 32-bit master separate for Tx and Rx

- Big or little endian data byte ordering

- Scatter/Gather capabilities

- Configurable number of Buffer-Descriptors

- Transmit/Receive dual port Synchronization RAMs

- Operate as internal configurable FIFOs with programmable threshold levels

- Configurable sizes up to 16kB

Block Diagram

Applications

- The EMAC-1G can be used tin any SoC design requiring Ethernet connectivity.

Deliverables

- Synthesizable Verilog RTL or FPGA netlist

- Testbench & sample test cases

- Simulation & synthesis scripts

- Documentation

Technical Specifications

Maturity

Production Proven

Availability

Now

Related IPs

- Gigabit Ethernet Media Access

- 10 Gigabit Ethernet Media Access Controller (10GEMAC)

- Gigabit Ethernet 802.3 MAC - Media Access Controller

- Multi-channel, multi-speed Ethernet universal media access control (MAC) and physical coding sublayer IP (UMAC)

- Tri-Mode Ethernet Media Access Controller (TEMAC)

- 10/100 Mb Media Access Controller