Freescale Semiconductor is the world’s leading provider of 32-bit controllers and processors based on Freescale’s ColdFire® Architecture have been deployed in over half a billion devices. You can quickly and cost-effectively create your own low-power, highly-integrated, 32-bit ASIC solutions implementing the ColdFire Architecture.

ASIC designs based on the ColdFire V2 Core are software compatible with all ColdFire standard products and cycle accurate with Freescale V2-based devices.

Code compatibility and a shared ecosystem mean easy migration not only from 8-bit to 32-bit CPUs and through emerging generations of the ColdFire Architecture, but also from module level integration to IP core level integration.

The entire ColdFire Family, including the V2 ColdFire Core and SPP, is supported by world-class development tools suites offered through leading tools developers. Development tools supporting ColdFire include Freescale’s CodeWarrior Special Edition software suite for ColdFire plus other professional tools from Freescale partners, including Green Hills Software, Wind River Systems, Accelerated Technology/Mentor Graphics, and many others.

ColdFire V2 Processor

Overview

Key Features

- Variable-length RISC, clock-multiplied core

- 166-MHz in typical 130-nm process

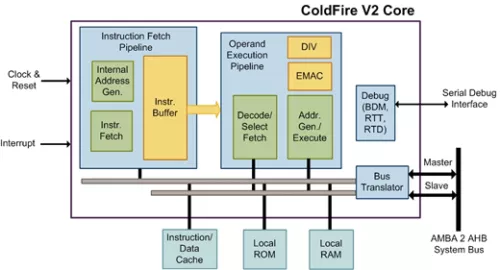

- Independent, decoupled pipelines: 2-stage instruction fetch pipeline (IFP); 2-stage operand execution pipeline (OEP); FIFO instruction buffer is the decoupling mechanism

- 16 user-accessible, 32-bit general purpose registers (GPRs)

- 32-bit data bus

- 32-bit address bus supporting 4-GB linear addressing range

- Sophisticated two-level branch acceleration mechanisms minimize change-of-flow execution time

- Background Debug Mode (BDM), Real-Time Trace (RTT), and Real-Time Debug (RTD) support

- Binary object code compatibility across the entire Freescale ColdFire Family

- Enhanced Multiply-Accumulate (EMAC) provides high-speed signal processing capabilities with four 40-bit accumulators and single-cycle instruction issue rate on 32-bit MAC operations

- Vector base register to relocate the exception-vector table

- Integrated cache controller; cache is direct-mapped, configurable as instruction, data, or split instruction/data cache

- Integrated SRAM controller

- 100% synthesizable and technology-independent design

- EDA tool-neutral packaging

Block Diagram

Video

Putting the ColdFire Family to Work for You

Deliverables

- The ColdFire V2 Processor is available in Verilog source RTL

- The deliverables include:

- Verilog source code

- Integration Testbench and Test-suite

- Comprehensive Documentation

- Scripts for simulation and synthesis with support for common EDA tools

Technical Specifications

Maturity

Silicon Proven

Availability

Now

Related IPs

- ColdFire V2 SPP5208 Processor Platform

- ColdFire V2 SPPC1 Processor Platform

- ARC HS34 32-bit processor core, ARC V2 ISA, for embedded applications

- ARC HS36 32-bit processor core, ARC V2 ISA, for embedded applications

- ARC HS44 32-bit, dual-issue processor core, ARC V2 ISA, for embedded applications

- ARC HS46 32-bit, dual-issue processor core, ARC V2 ISA, for embedded applications